# User Guide for Config Tools for i.MX

# **Contents**

| Chapter 1 Introduction                                     | 5  |

|------------------------------------------------------------|----|

| 1.1 Features                                               | 5  |

| 1.2 Versions                                               |    |

| 1.3 Tools localization                                     |    |

|                                                            |    |

| Chapter 2 User Interface                                   | 7  |

| 2.1 Start Development wizard                               |    |

| 2.2 Creating, saving, and opening a configuration          |    |

| 2.2.1 Creating a new configuration                         |    |

| 2.2.1.1 Creating a new standalone configuration            |    |

| 2.2.2 Saving a configuration                               |    |

| 2.2.3 Opening an existing configuration                    |    |

| 2.2.4 User templates                                       |    |

| 2.2.5 Importing sources                                    |    |

| 2.2.5.1 Importing configuration                            |    |

| 2.2.5.2 Importing Board/Kit Configuration                  |    |

| 2.2.6 Exporting sources                                    |    |

| 2.3 Menu bar                                               |    |

| 2.4 Toolbar                                                |    |

| 2.4.1 Config tools overview                                |    |

| 2.4.2 Update code                                          |    |

| 2.4.3 Functional groups                                    |    |

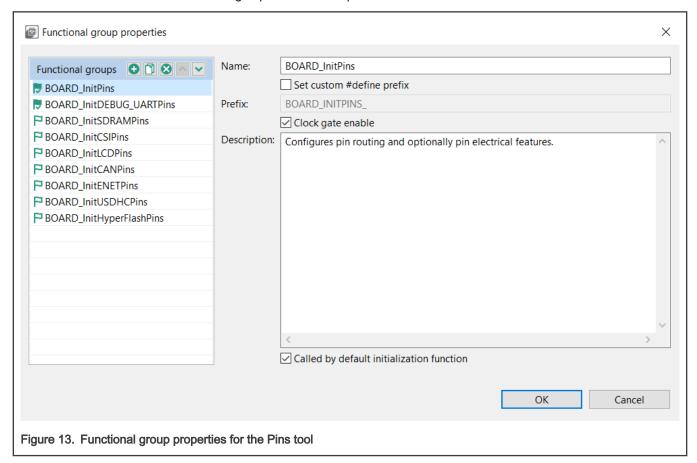

| 2.4.3.1 Functional group properties                        |    |

| 2.4.4 Undo/Redo actions                                    |    |

| 2.5 Preferences                                            |    |

| 2.6 Configuration preferences                              |    |

| 2.7 Problems view                                          |    |

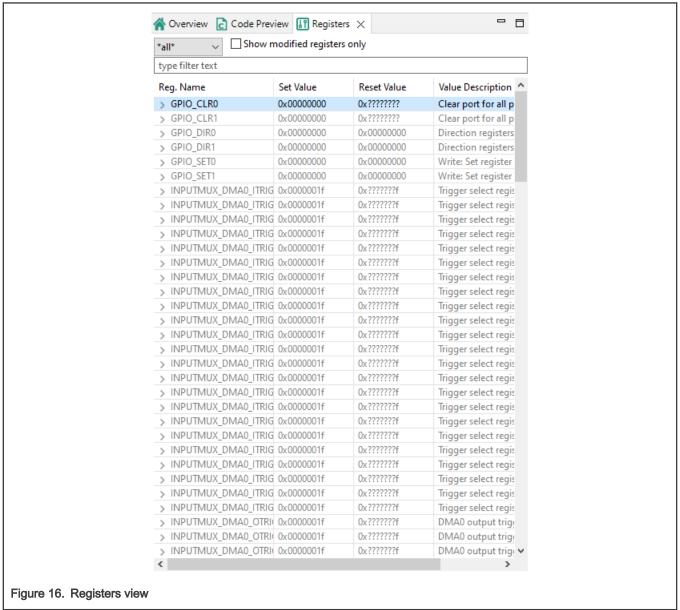

| 2.8 Registers view                                         |    |

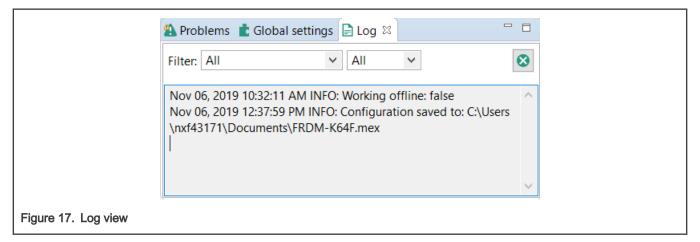

| 2.9 Log view                                               |    |

|                                                            |    |

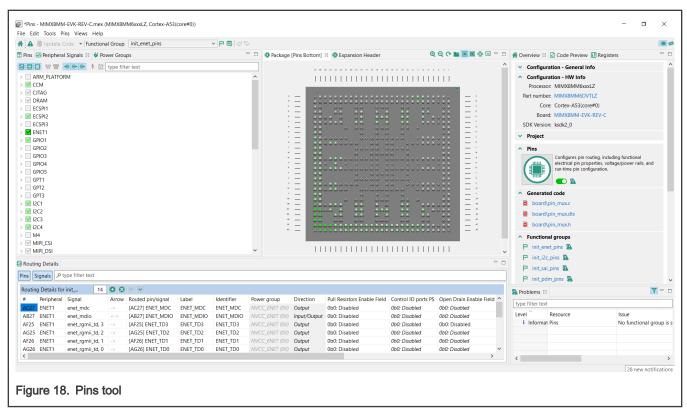

| Chapter 3 Pins Tool                                        |    |

| 3.1 Pins routing principle                                 |    |

| 3.1.1 Beginning with pin/internal signal selection         |    |

| 3.1.2 Routing of peripheral signals                        |    |

| 3.2 Example usage                                          |    |

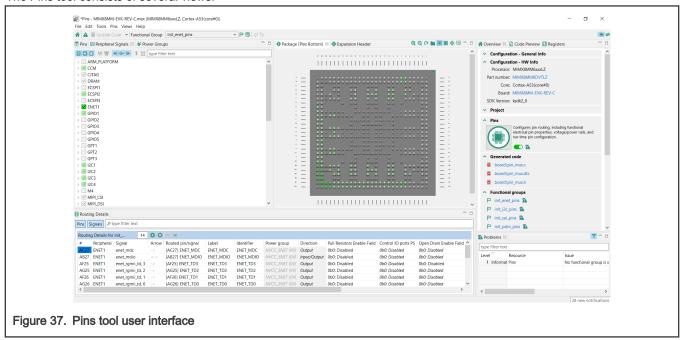

| 3.3 User interface                                         | 38 |

| 3.3.1 Pins view                                            |    |

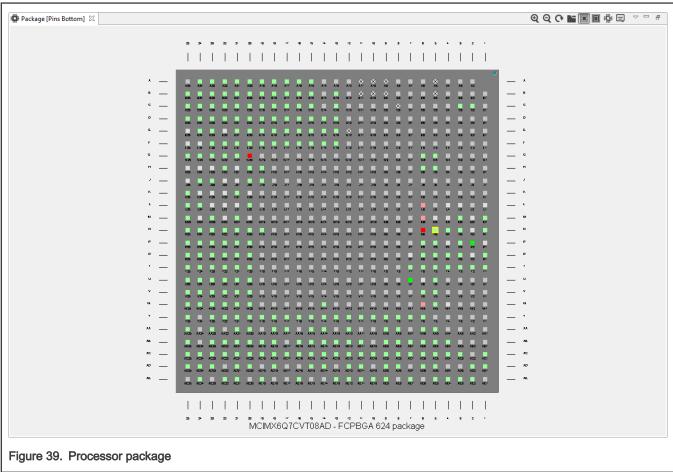

| 3.3.2 Package                                              |    |

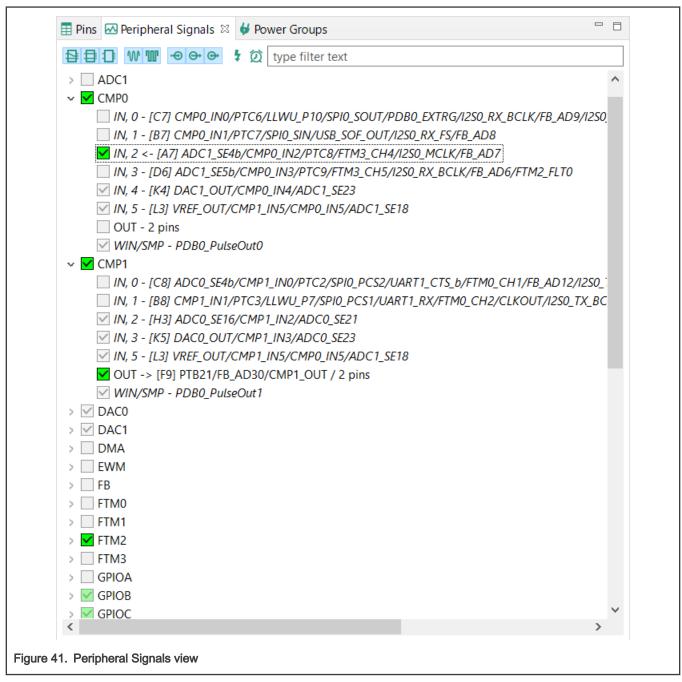

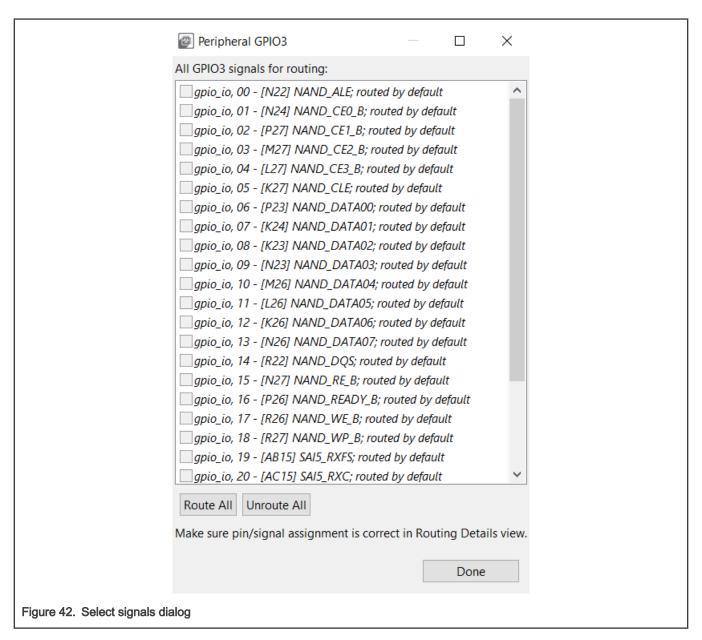

| 3.3.3 Peripheral Signals view                              |    |

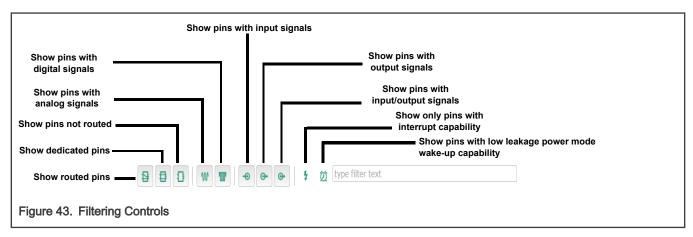

| 3.3.3.1 Filtering in the Pins and Peripheral Signals views |    |

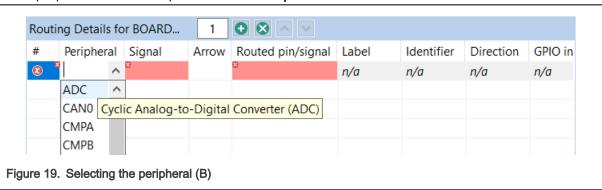

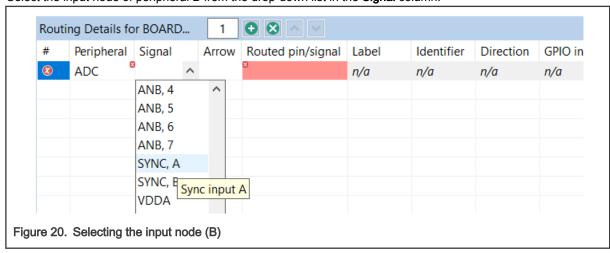

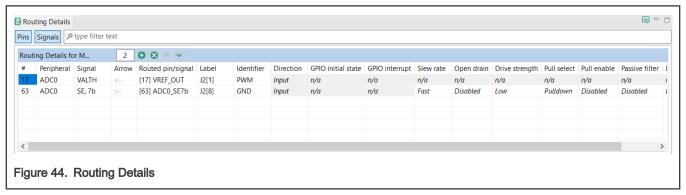

| 3.3.4 Routing Details view                                 |    |

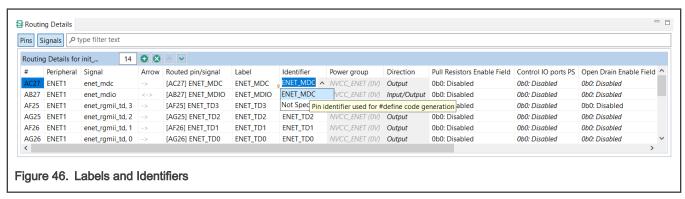

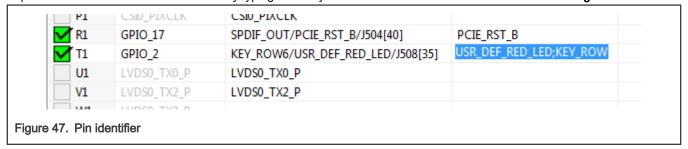

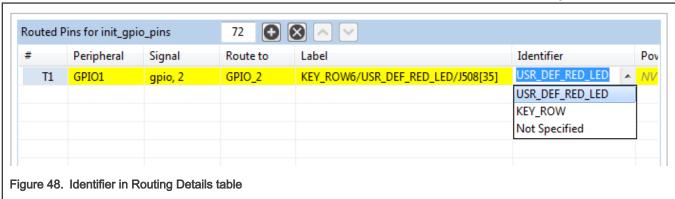

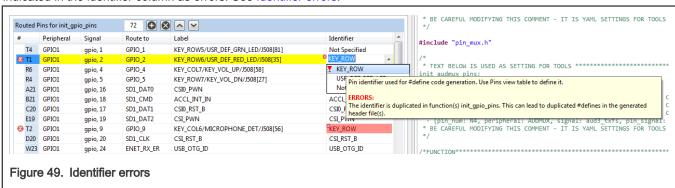

| 3.3.4.1 Labels and identifiers                             |    |

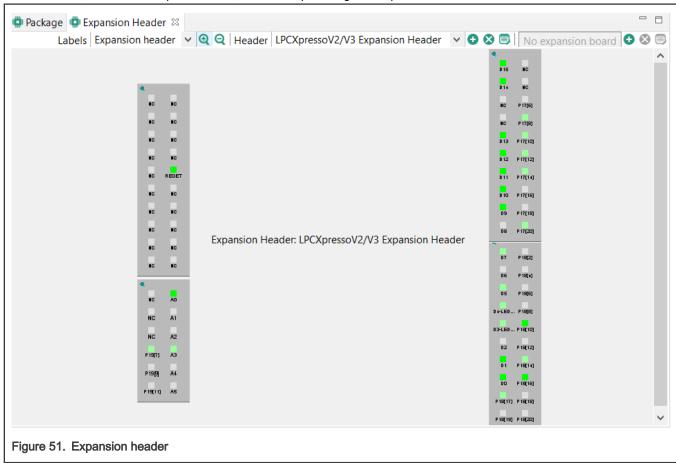

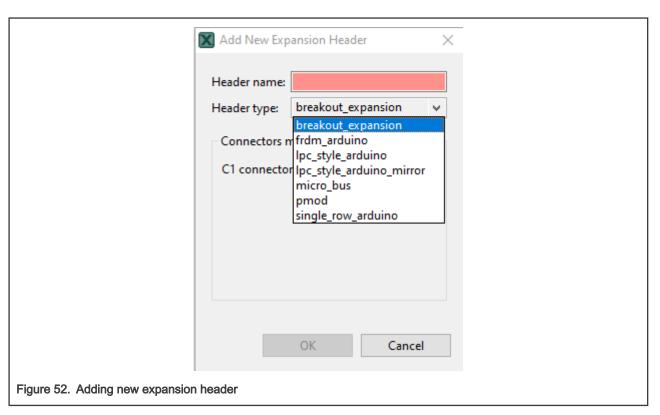

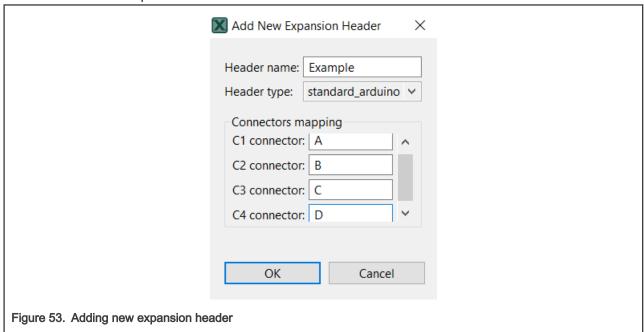

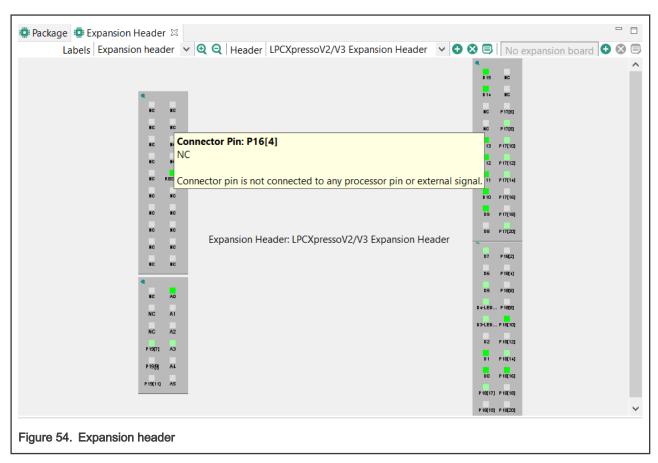

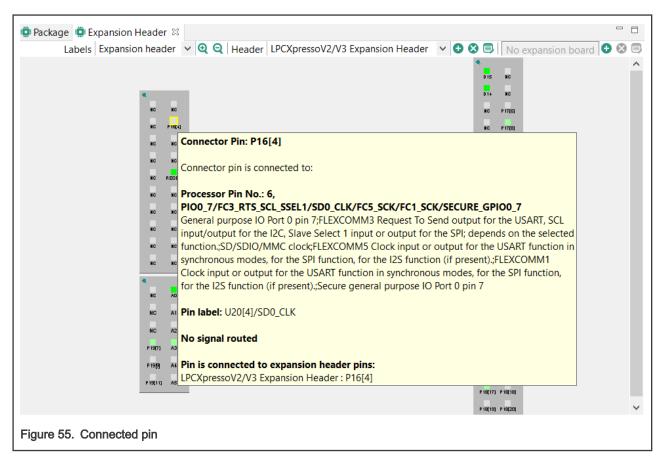

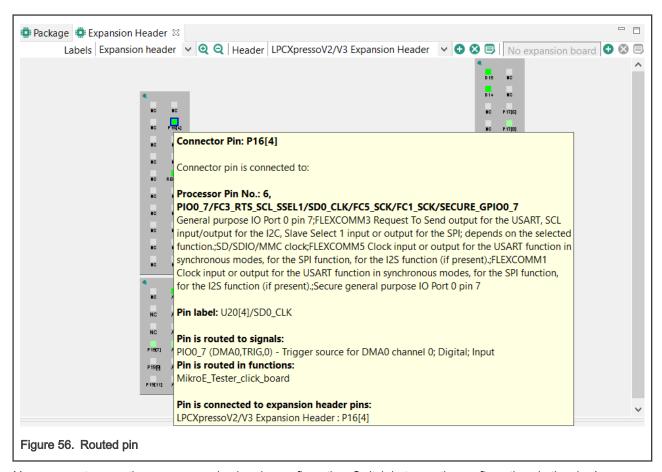

| 3.3.5 Expansion Header                                     |    |

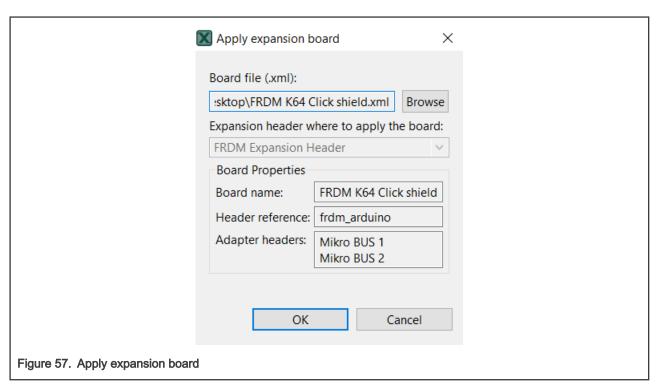

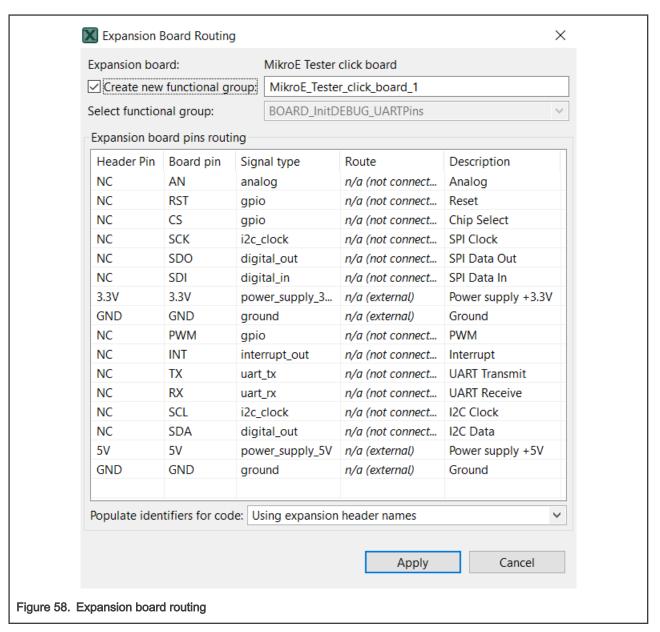

| 3.3.5.1 Expansion Board                                    |    |

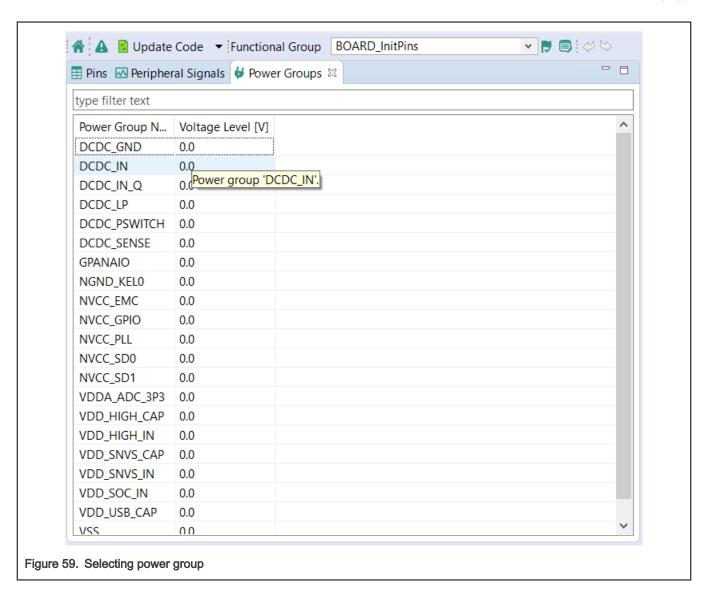

| 3.3.6 Power groups                                         |    |

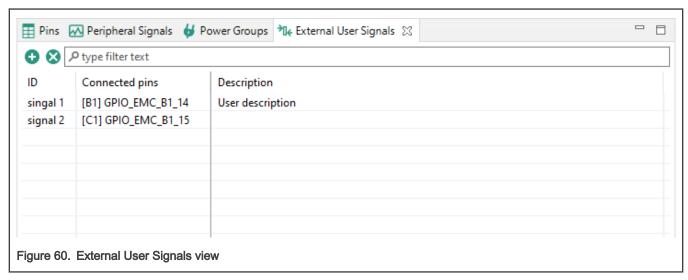

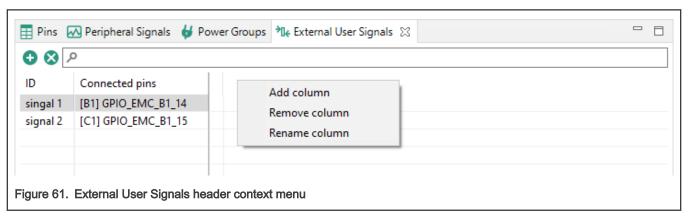

| 3.3.7 External User Signals view                           |    |

| 3.3.8 Functions                                            |    |

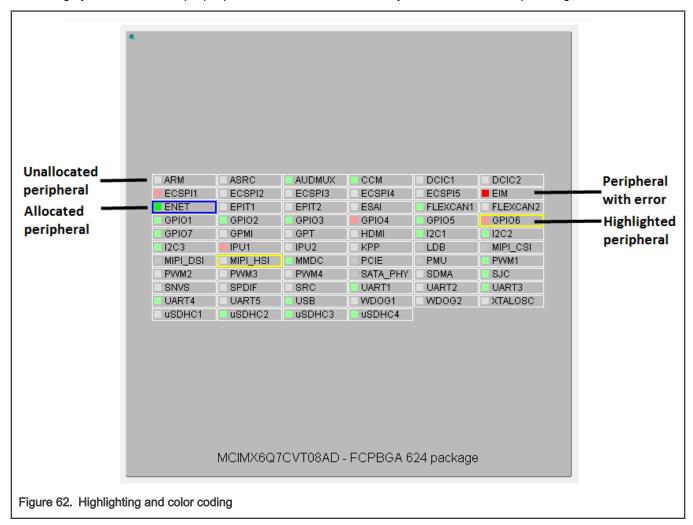

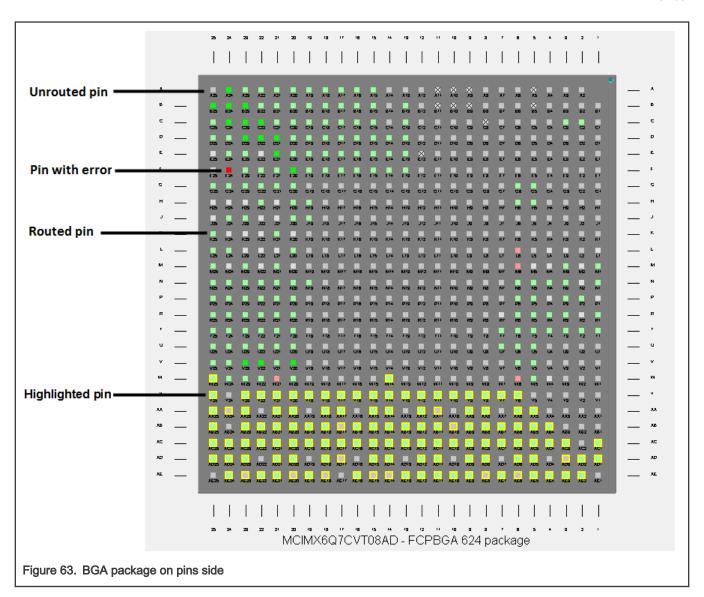

| 3.3.9 Highlighting and color coding                        |    |

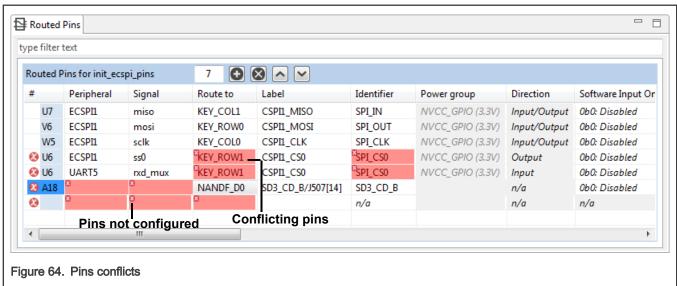

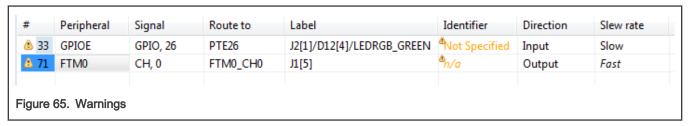

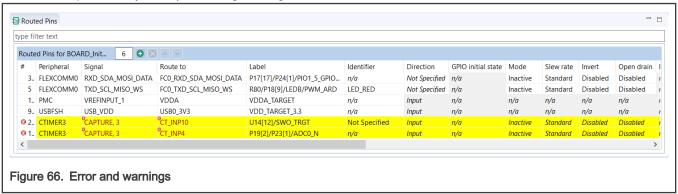

| 3.4 Errors and warnings                                    |    |

| <b>∵</b>                                                   |    |

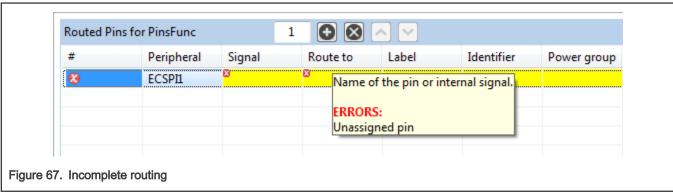

| 3.4.1 Incomplete routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

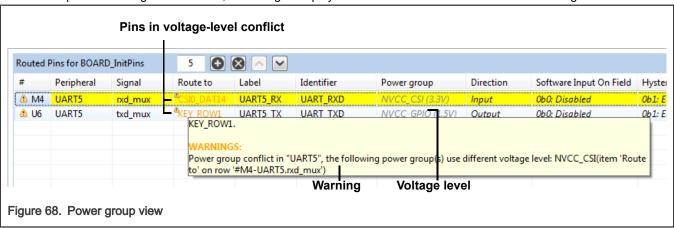

| 3.4.2 Power groups voltage level conflicts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 61                                                                                                                                                                          |

| 3.5 Code generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61                                                                                                                                                                          |

| 3.6 Using pins definitions in code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62                                                                                                                                                                          |

| 3.7 Full initialization of pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |

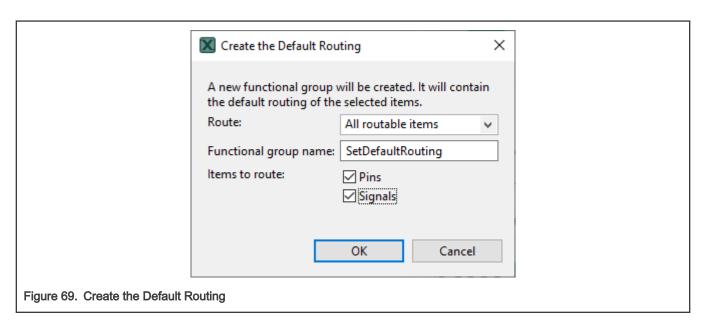

| 3.8 Create Default Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |

| Chapter 4 DDR Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                             |

| 4.1 Create a new DDR tool project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                             |

| 4.2 DDR configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                             |

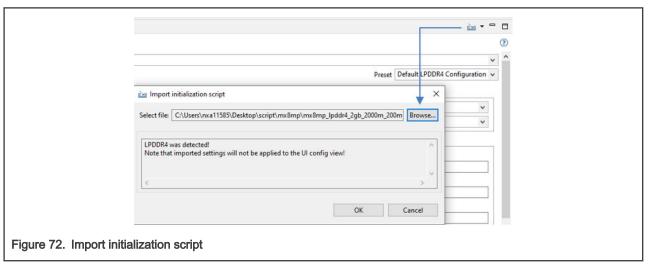

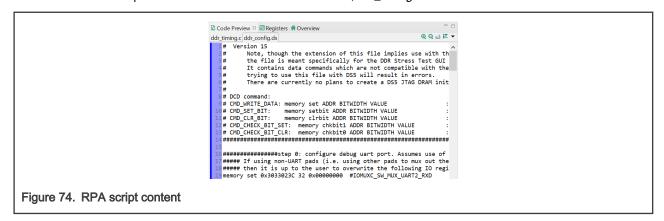

| 4.2.1 Import initialization script                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                             |

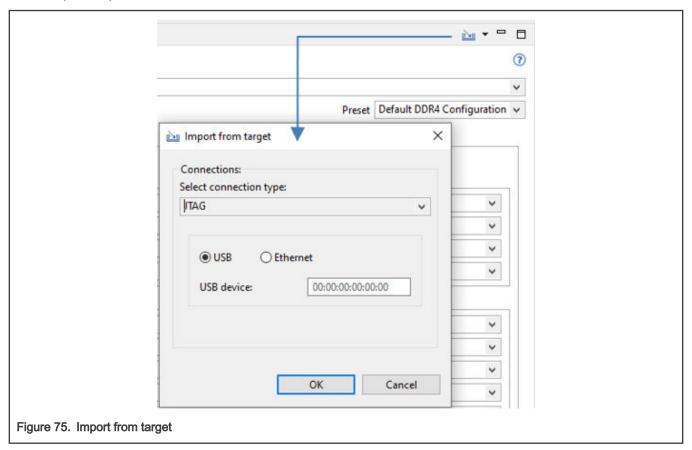

| 4.2.2 Import from target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                             |

| 4.2.3 Enable manual configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                             |

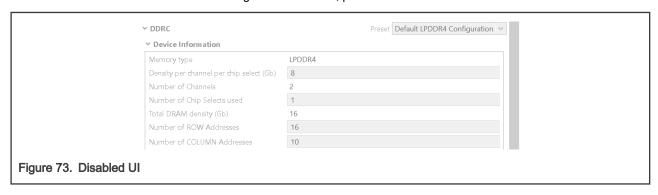

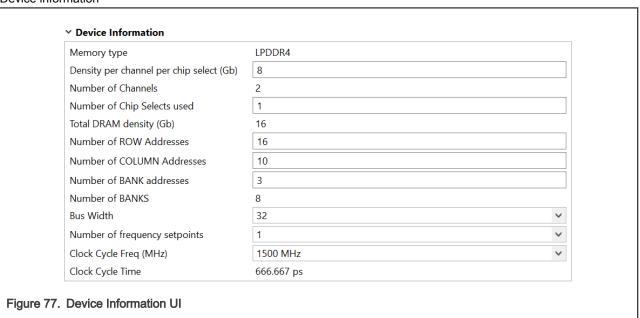

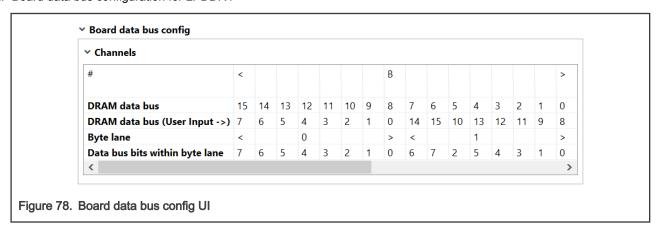

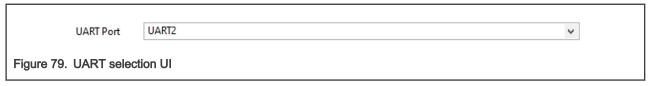

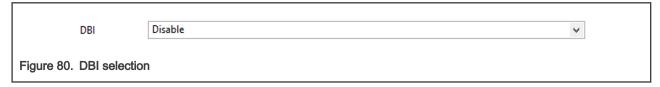

| 4.2.4 UI configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                             |

| 4.2.5 Code generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                             |

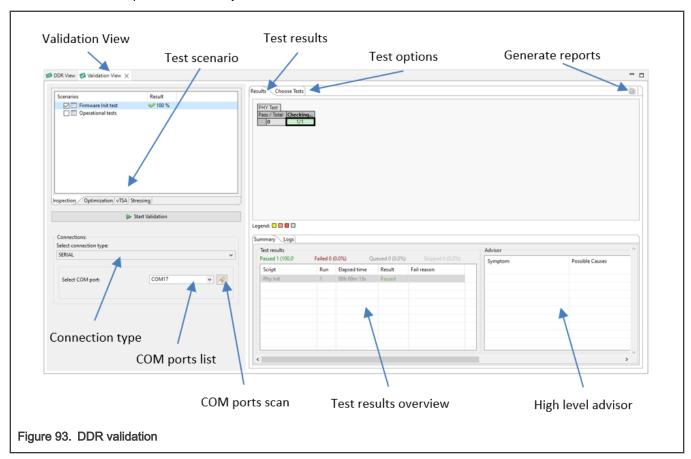

| 4.3 DDR validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                             |

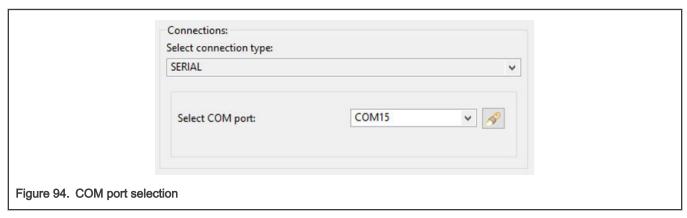

| 4.3.1 Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                             |

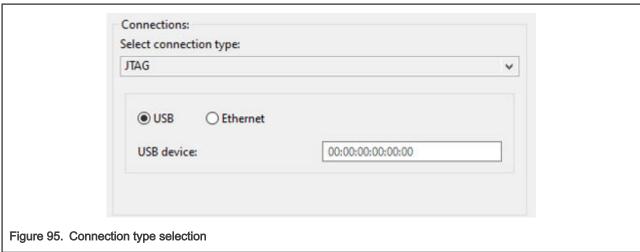

| 4.3.1.2 Boards with JTAG connection available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |

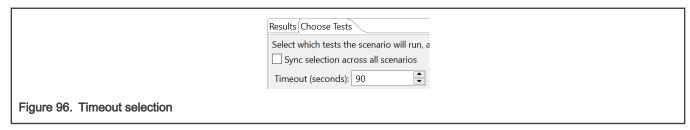

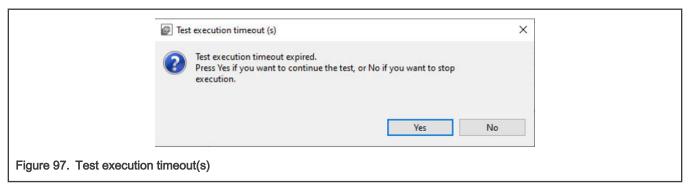

| 4.3.2 Test scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                             |

| 4.3.2.1 Inspection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                             |

| 4.3.2.2 Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                             |

| 4.3.2.3 vTSA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                             |

| 4.3.2.4 Stressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                             |

| 4.4 FAQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82                                                                                                                                                                          |

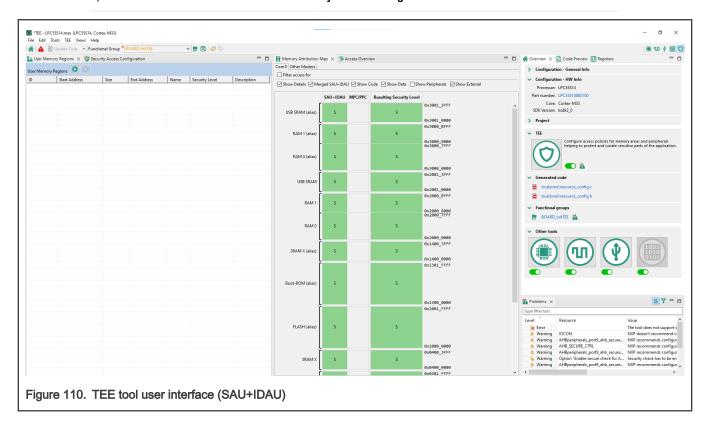

| Chapter 5 Trusted Execution Environment Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                             |

| Chapter 5 Trusted Execution Environment Tool 5.1 AHB with security extension-enabled devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83                                                                                                                                                                          |

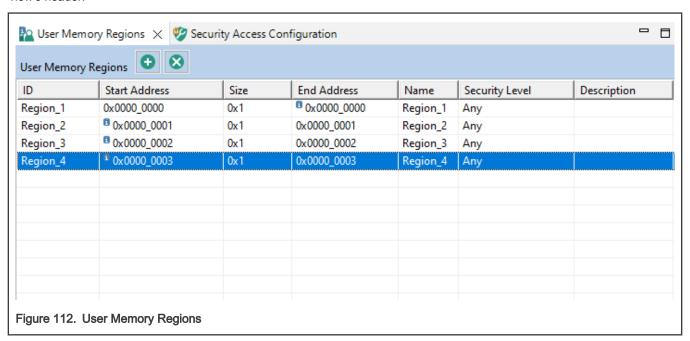

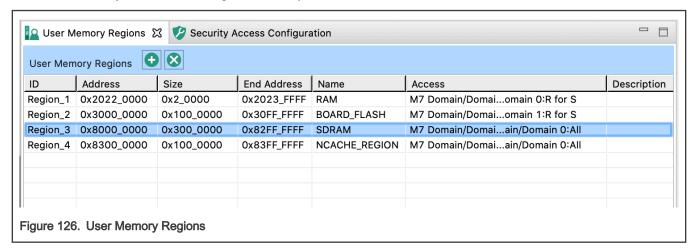

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83<br>83                                                                                                                                                                    |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |

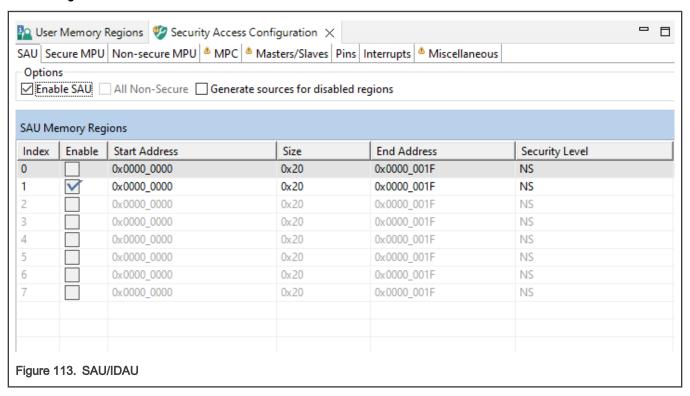

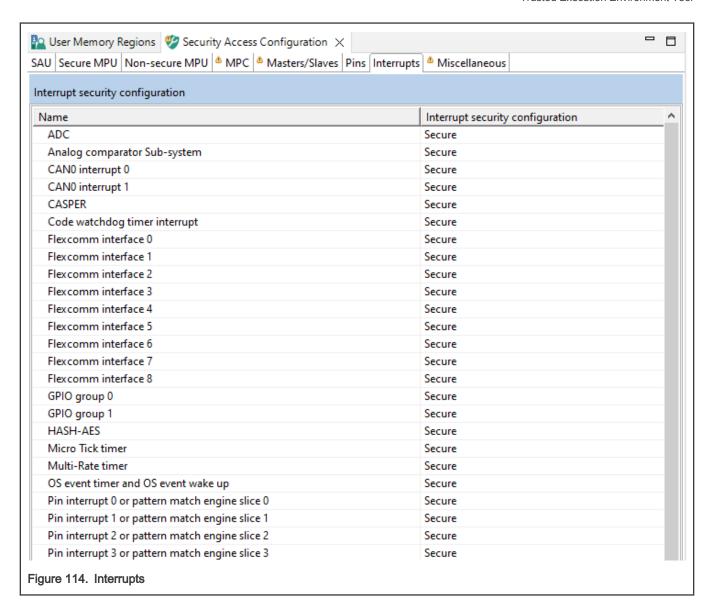

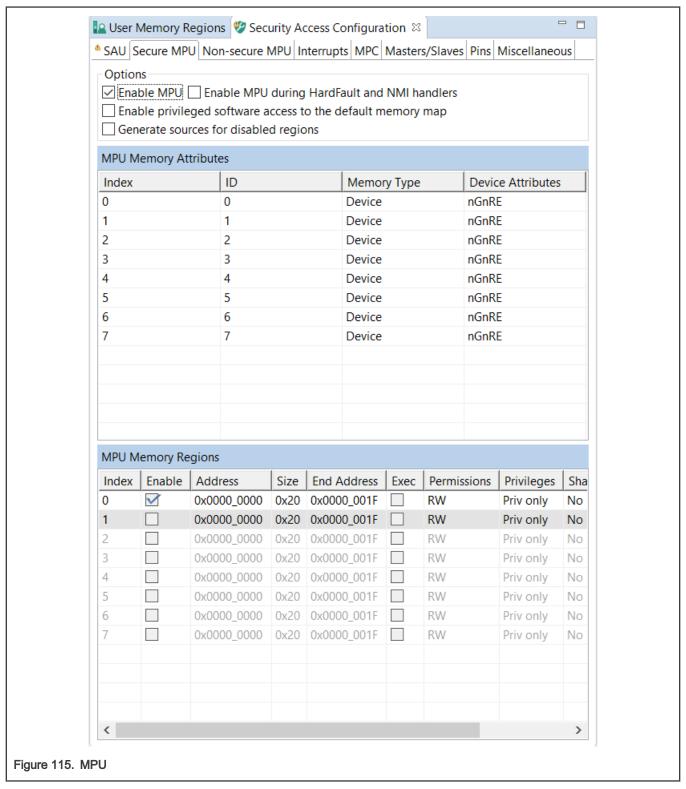

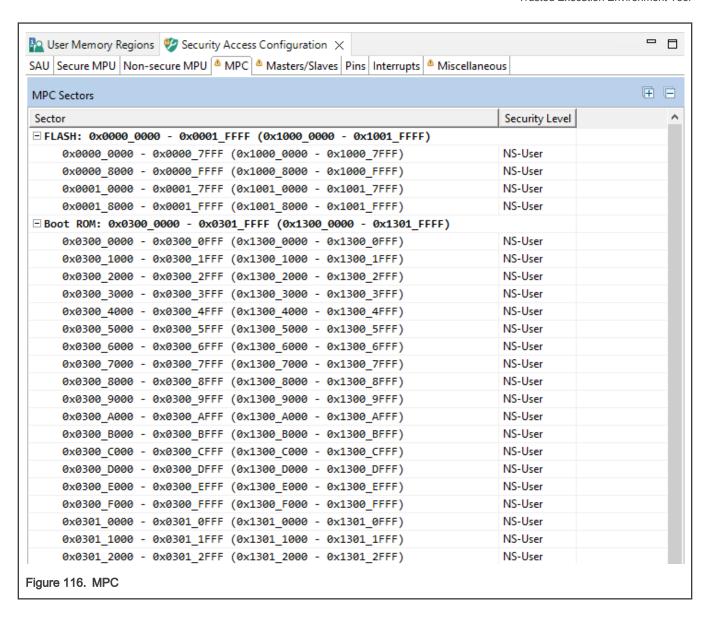

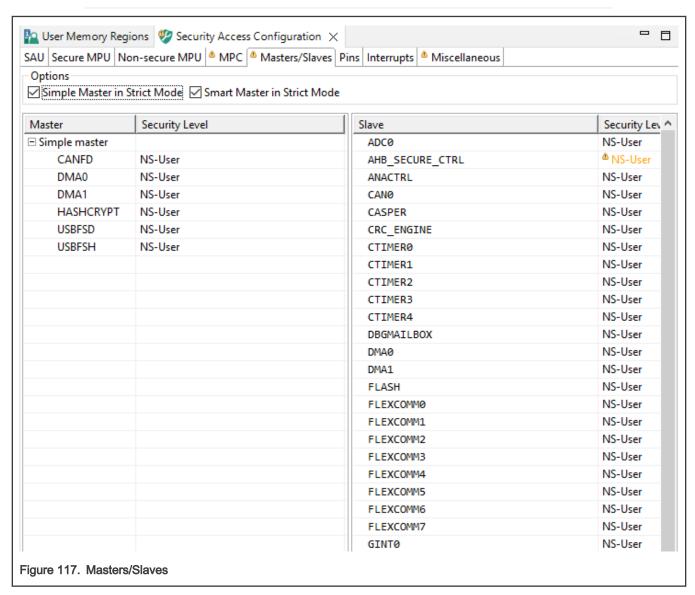

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.4 MPC  5.1.2.5 Masters/Slaves                                                                                                                                                                                                                                                                                                                                                                                 | 83 83 84 84 85 85 86 88 89                                                                                                                                                  |

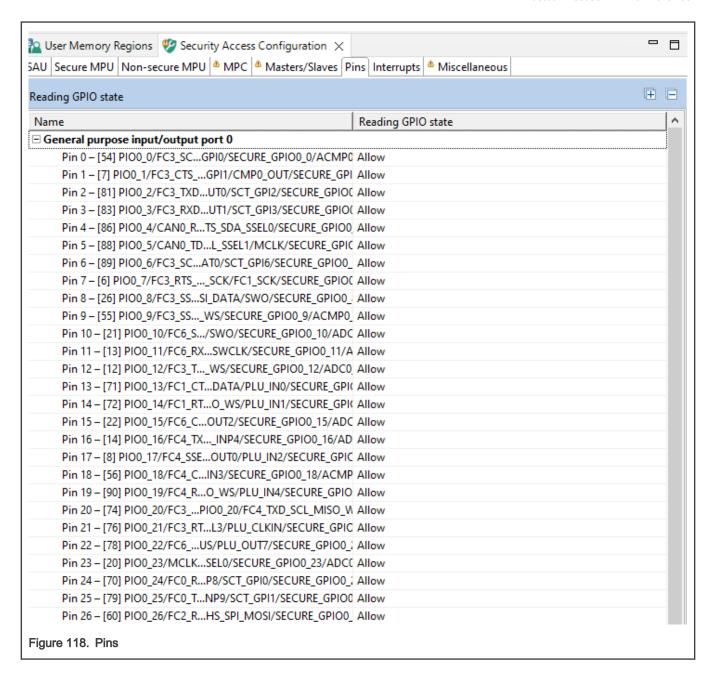

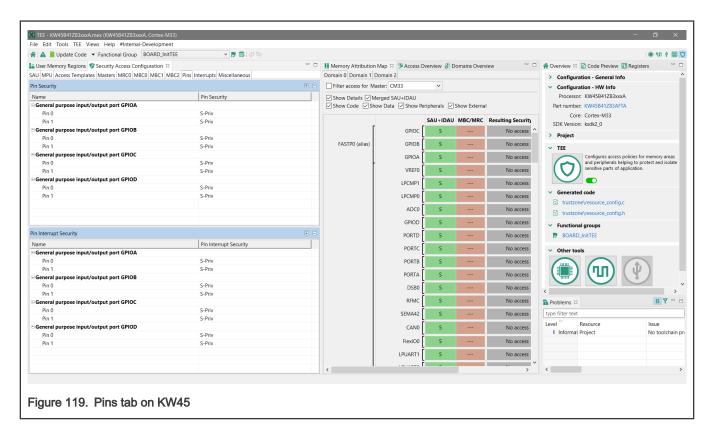

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83 83 84 84 85 85 86 89 90                                                                                                                                                  |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83 83 84 84 85 85 86 88 89 90                                                                                                                                               |

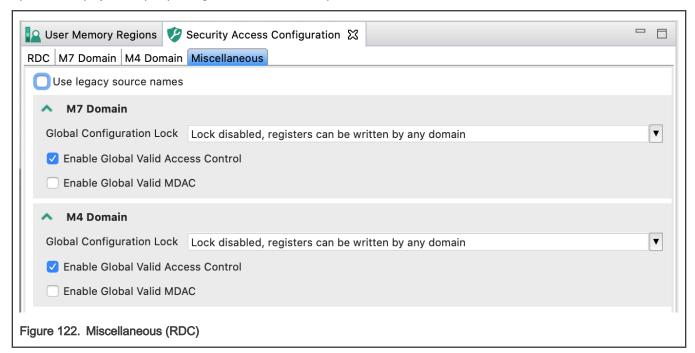

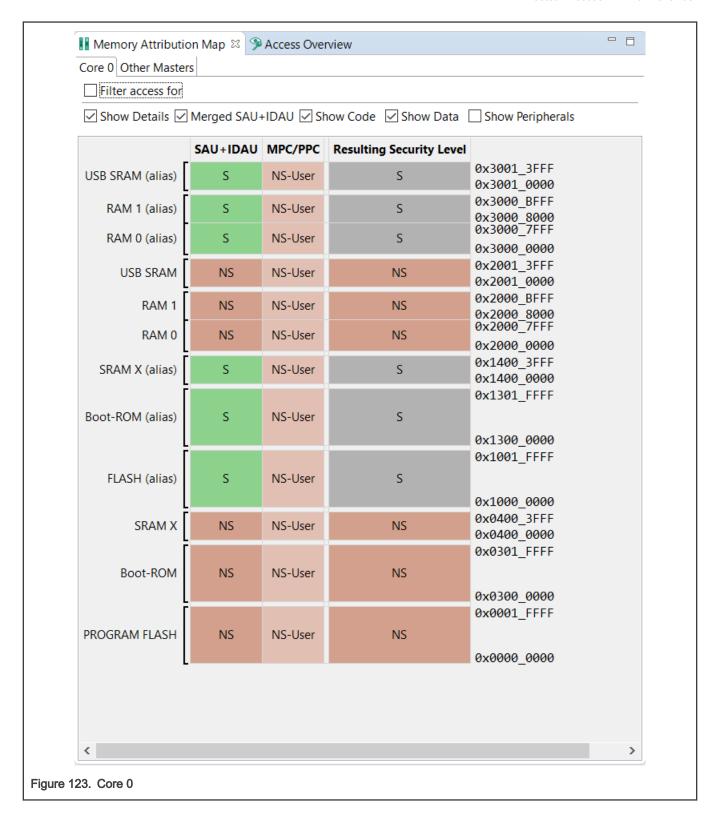

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.4 MPC  5.1.2.5 Masters/Slaves  5.1.2.6 Pins  5.1.2.7 Miscellaneous  5.1.3 Memory attribution map                                                                                                                                                                                                                                                                                                              | 83 83 84 84 85 85 86 89 90 93                                                                                                                                               |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.4 MPC  5.1.2.5 Masters/Slaves  5.1.2.6 Pins  5.1.2.7 Miscellaneous  5.1.3 Memory attribution map  5.1.3.1 Core 0  5.1.3.2 Other masters  5.1.4 Access Overview                                                                                                                                                                                                                                                | 83 83 84 84 85 85 89 90 90 93                                                                                                                                               |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices 5.1.1 User Memory Regions view 5.1.2 Security Access Configuration view 5.1.2.1 SAU                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 83 83 84 84 85 85 86 89 90 90 93 93                                                                                                                                         |

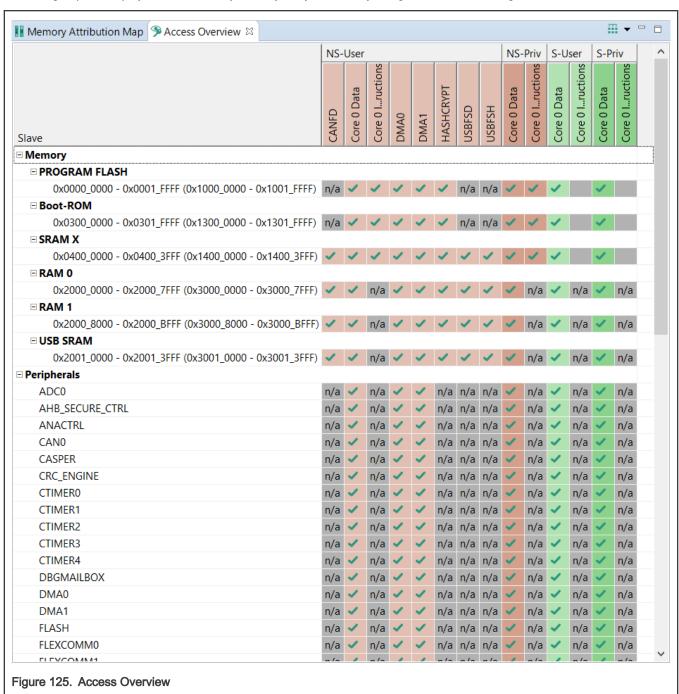

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices 5.1.1 User Memory Regions view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83 83 84 84 85 85 86 89 90 90 93 94 94                                                                                                                                      |

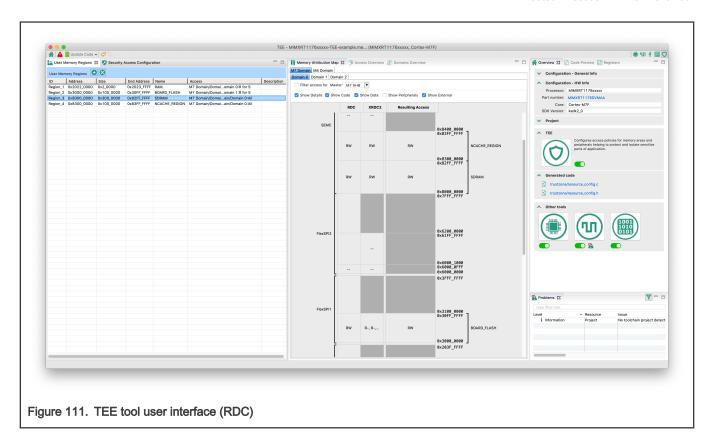

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.4 MPC  5.1.2.5 Masters/Slaves  5.1.2.6 Pins  5.1.2.7 Miscellaneous  5.1.3 Memory attribution map  5.1.3.1 Core 0  5.1.3.2 Other masters  5.1.4 Access Overview  5.1.5 Code generation  5.2 RDC-enabled devices  5.2.1 User Memory Regions view                                                                                                                                                                | 83 83 84 84 85 85 86 88 89 90 91 93 94 94                                                                                                                                   |

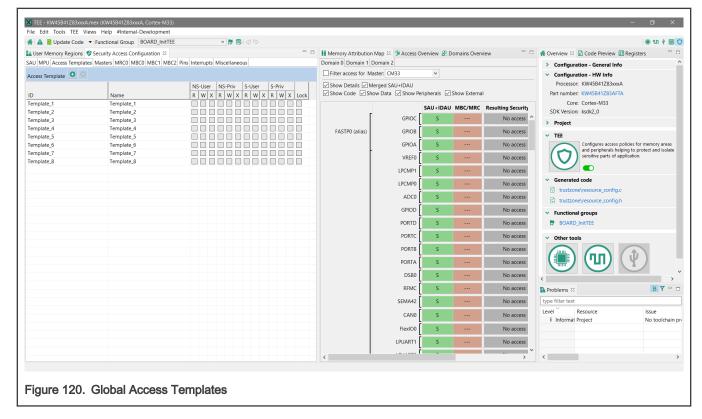

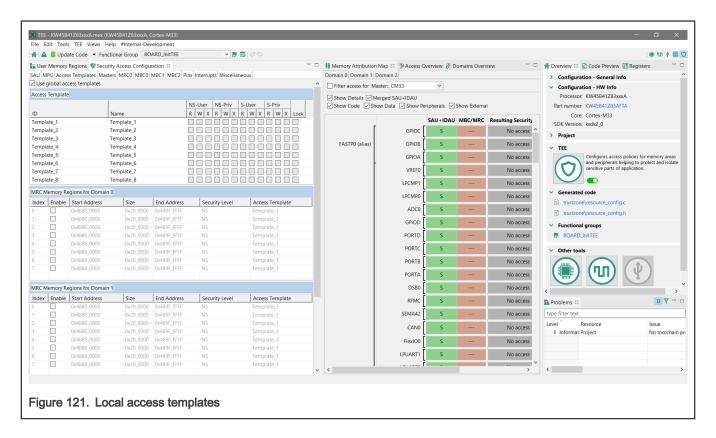

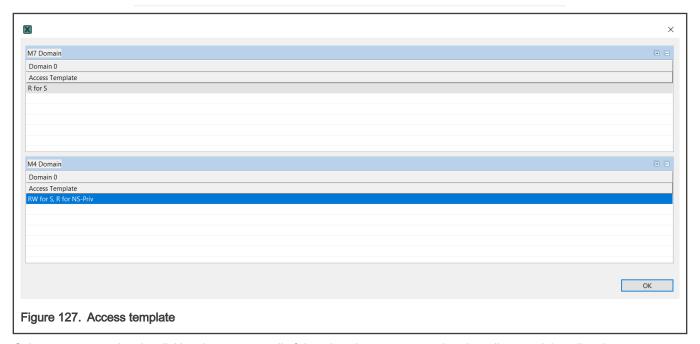

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.4 MPC  5.1.2.5 Masters/Slaves  5.1.2.6 Pins  5.1.2.7 Miscellaneous  5.1.3 Memory attribution map  5.1.3.1 Core 0  5.1.3.2 Other masters  5.1.4 Access Overview  5.1.5 Code generation  5.2 RDC-enabled devices  5.2.1 User Memory Regions view  5.2.1.1 Access templates                                                                                                                                      | 83 83 84 84 84 85 85 86 88 90 90 93 94 94 99 99                                                                                                                             |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.4 MPC  5.1.2.5 Masters/Slaves  5.1.2.6 Pins  5.1.2.7 Miscellaneous  5.1.3 Memory attribution map  5.1.3.1 Core 0  5.1.3.2 Other masters  5.1.4 Access Overview  5.1.5 Code generation  5.2 RDC-enabled devices  5.2.1 User Memory Regions view  5.2.1.1 Access templates  5.2.2 Security Access Configuration view                                                                                            | 83 83 84 84 84 85 85 86 88 89 90 91 93 94 95 95                                                                                                                             |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.4 MPC  5.1.2.5 Masters/Slaves  5.1.2.6 Pins  5.1.2.7 Miscellaneous  5.1.3 Memory attribution map  5.1.3.1 Core 0  5.1.3.2 Other masters  5.1.4 Access Overview  5.1.5 Code generation  5.2 RDC-enabled devices  5.2.1 User Memory Regions view  5.2.1.1 Access templates  5.2.2 Security Access Configuration view  5.2.2.1 RDC                                                                               | 83 83 84 84 84 85 85 86 88 89 90 90 93 93 94 94 95 97 97 98                                                                                                                 |

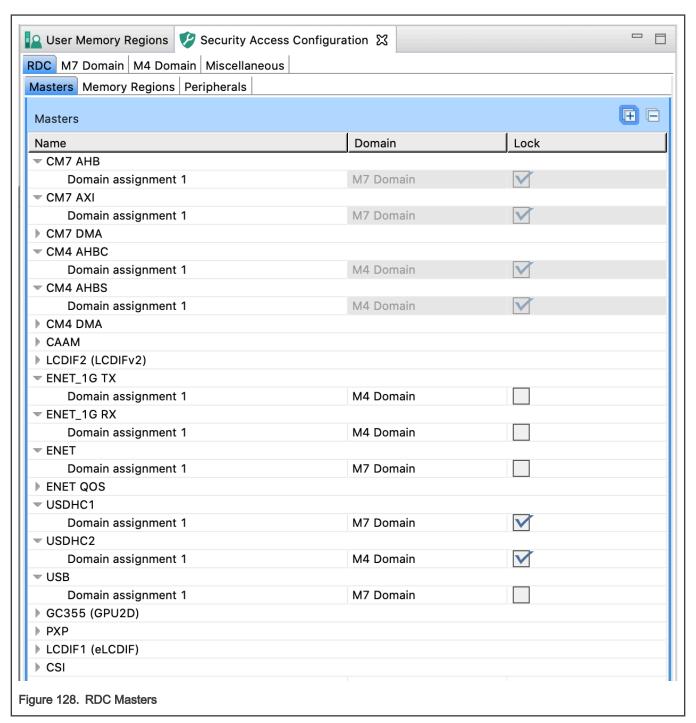

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices 5.1.1 User Memory Regions view 5.1.2 Security Access Configuration view 5.1.2.1 SAU 5.1.2.2 Interrupts 5.1.2.3 Secure/Non-secure MPU 5.1.2.4 MPC 5.1.2.5 Masters/Slaves 5.1.2.6 Pins 5.1.2.7 Miscellaneous 5.1.3 Memory attribution map 5.1.3.1 Core 0 5.1.3.2 Other masters 5.1.4 Access Overview 5.1.5 Code generation 5.2 RDC-enabled devices 5.2.1 User Memory Regions view 5.2.1.1 Access templates 5.2.2 Security Access Configuration view 5.2.2.1 RDC 5.2.2.1.1 RDC Masters                                                                            | 83 83 84 84 85 85 86 88 89 90 90 93 94 94 95 95 97 98                                                                                                                       |

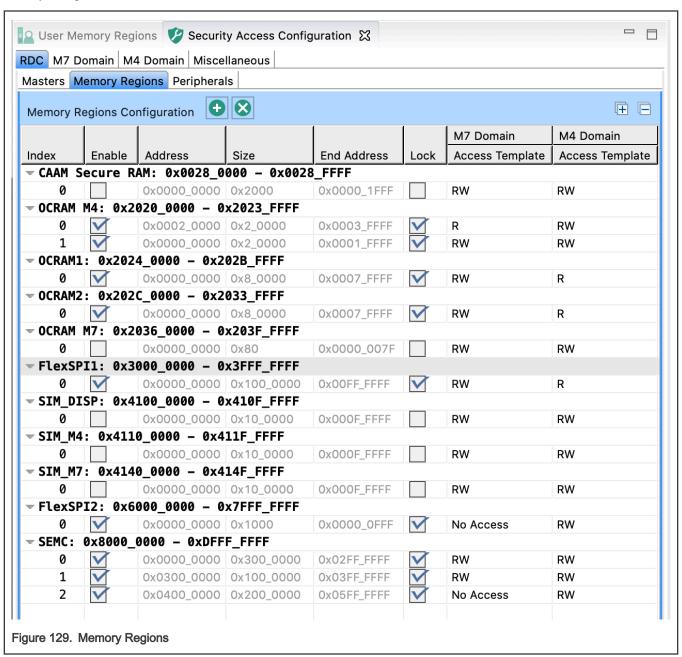

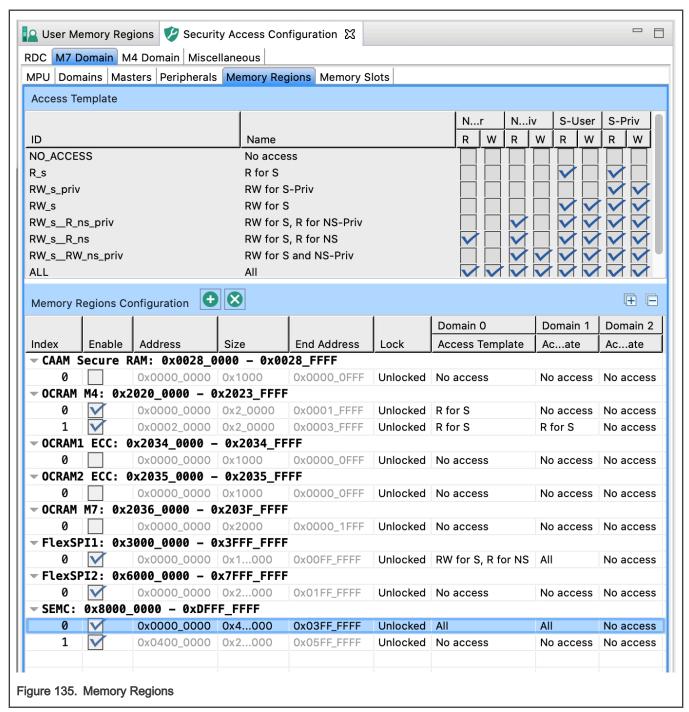

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.4 MPC  5.1.2.5 Masters/Slaves  5.1.2.6 Pins  5.1.2.7 Miscellaneous  5.1.3 Memory attribution map  5.1.3.1 Core 0  5.1.3.2 Other masters  5.1.4 Access Overview  5.1.5 Code generation  5.2 RDC-enabled devices  5.2.1 User Memory Regions view  5.2.2.1 RDC  5.2.2.1 RDC Masters  5.2.2.1.2 Memory Regions                                                                                                    | 83 83 84 84 84 85 85 86 88 89 90 90 93 94 94 95 97 98                                                                                                                       |

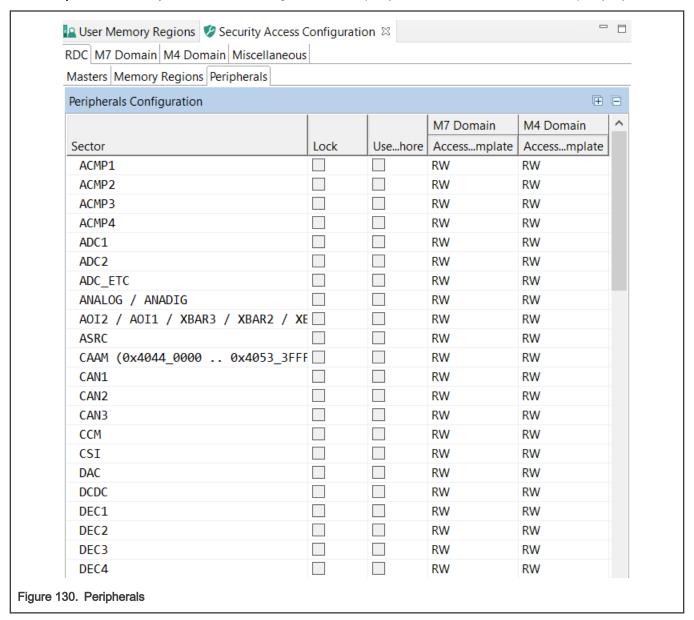

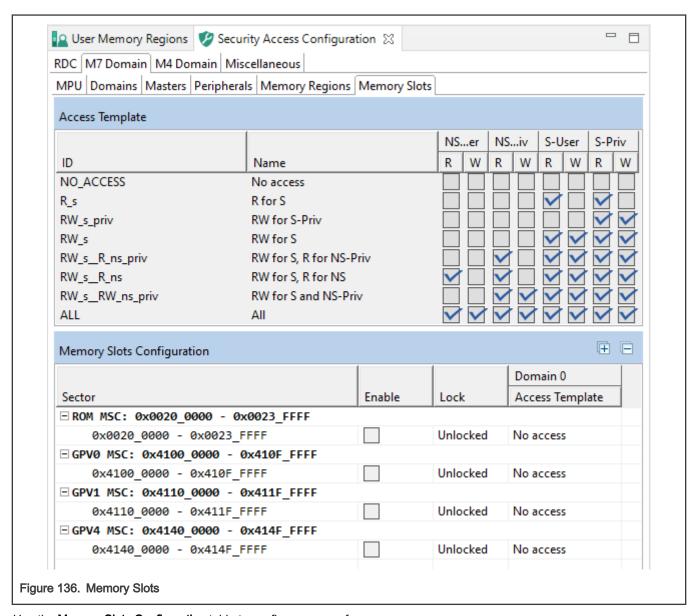

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.5 Masters/Slaves  5.1.2.6 Pins  5.1.2.7 Miscellaneous  5.1.3 Memory attribution map  5.1.3.1 Core 0  5.1.3.2 Other masters  5.1.4 Access Overview  5.1.5 Code generation  5.2 RDC-enabled devices  5.2.1 User Memory Regions view  5.2.2.1 RDC  5.2.2.1 RDC Masters  5.2.2.1.2 Memory Regions  5.2.2.1.2 Memory Regions  5.2.2.1.3 Peripherals                                                                | 83 83 84 84 84 85 85 86 88 89 90 90 93 94 94 94 95 97 100 100 100 100                                                                                                       |

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.4 MPC  5.1.2.5 Masters/Slaves  5.1.2.7 Miscellaneous  5.1.3 Memory attribution map  5.1.3.1 Core 0  5.1.3.2 Other masters  5.1.4 Access Overview  5.1.5 Code generation  5.2 RDC-enabled devices  5.2.1 User Memory Regions view  5.2.1.1 Access templates  5.2.2 Security Access Configuration view  5.2.2.1 RDC  5.2.2.1.2 Memory Regions  5.2.2.1.3 Peripherals  5.2.2.2 XRDC2 Domains view                | 83 83 84 84 84 85 85 86 88 89 90 91 93 94 94 95 97 97 97 98 99 100 100 100 100                                                                                              |

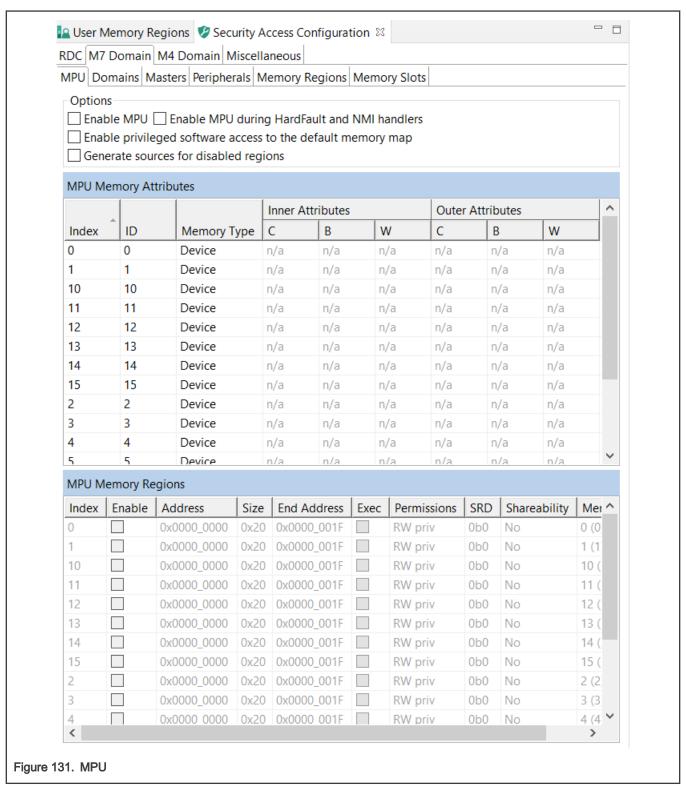

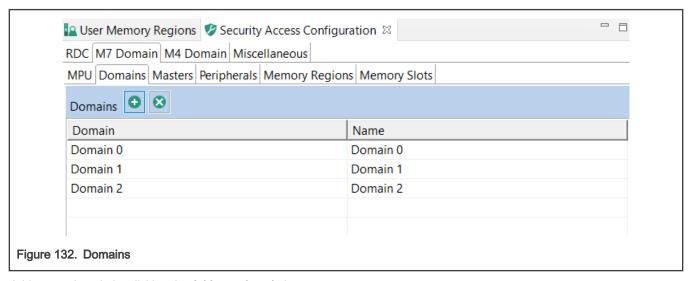

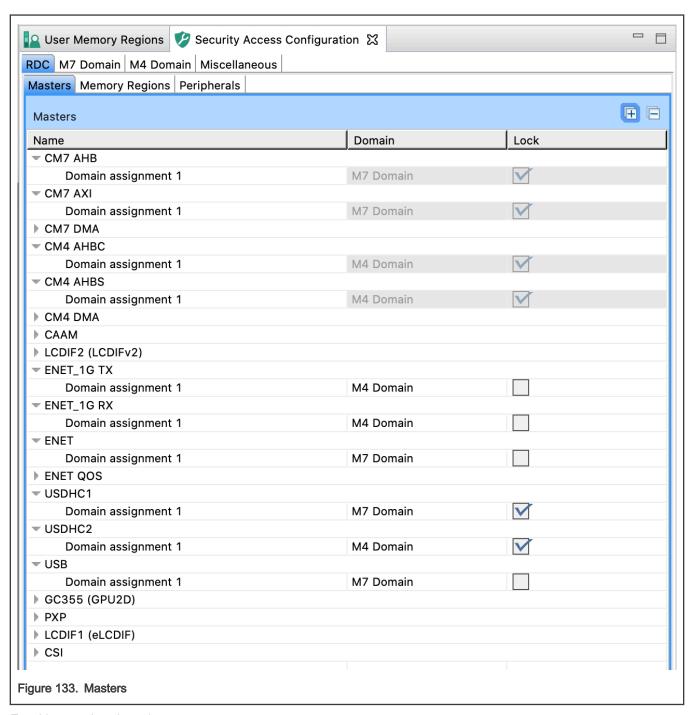

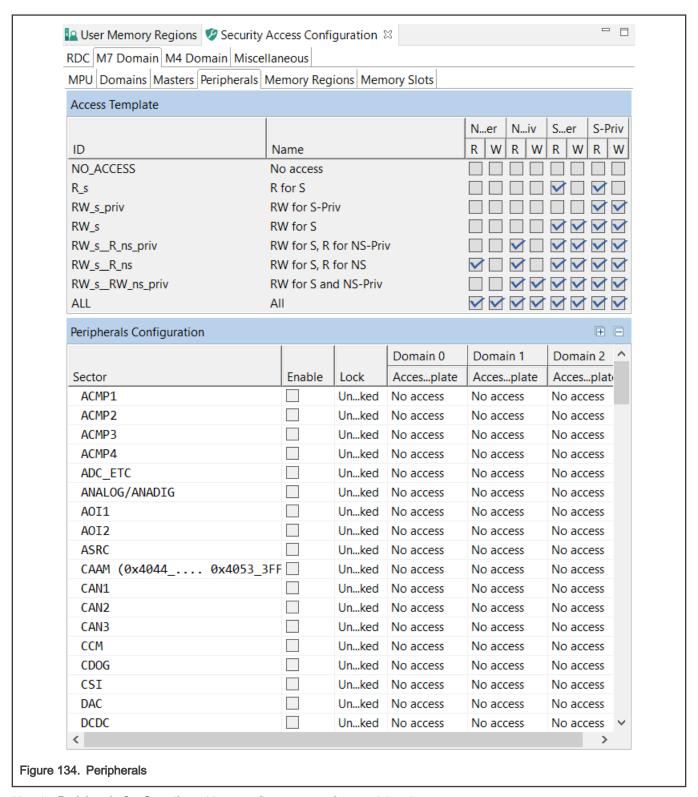

| Chapter 5 Trusted Execution Environment Tool  5.1 AHB with security extension-enabled devices  5.1.1 User Memory Regions view  5.1.2 Security Access Configuration view  5.1.2.1 SAU  5.1.2.2 Interrupts  5.1.2.3 Secure/Non-secure MPU  5.1.2.4 MPC  5.1.2.5 Masters/Slaves  5.1.2.7 Miscellaneous  5.1.3 Memory attribution map  5.1.3.1 Core 0  5.1.3.2 Other masters  5.1.4 Access Overview  5.1.5 Code generation  5.2 RDC-enabled devices  5.2.1 User Memory Regions view  5.2.1.1 Access templates  5.2.2 Security Access Configuration view  5.2.2.1 RDC  5.2.2.1.2 Memory Regions  5.2.2.1.3 Peripherals  5.2.2.2 XRDC2 Domains view  5.2.2.2.1 MPU | 83         84         85         86         88         90         93         94         95         97         98         99         100         100         102         103 |

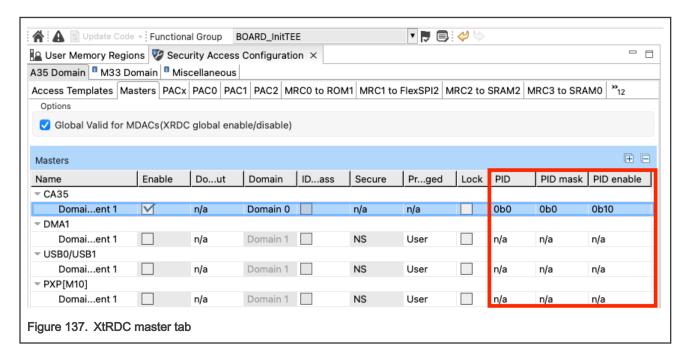

| 5.2.2.3 Masters                                                                      | 106 |

|--------------------------------------------------------------------------------------|-----|

| 5.2.2.2.4 Peripherals                                                                |     |

| 5.2.2.5 Memory Regions                                                               |     |

| 5.2.2.2.6 Memory Slots                                                               |     |

| 5.2.2.3 XRDC (eXtended Trusted Resource Domain Controller) on Cortex-A35 in i.MX8 UL |     |

| 5.2.2.3.1 Masters                                                                    |     |

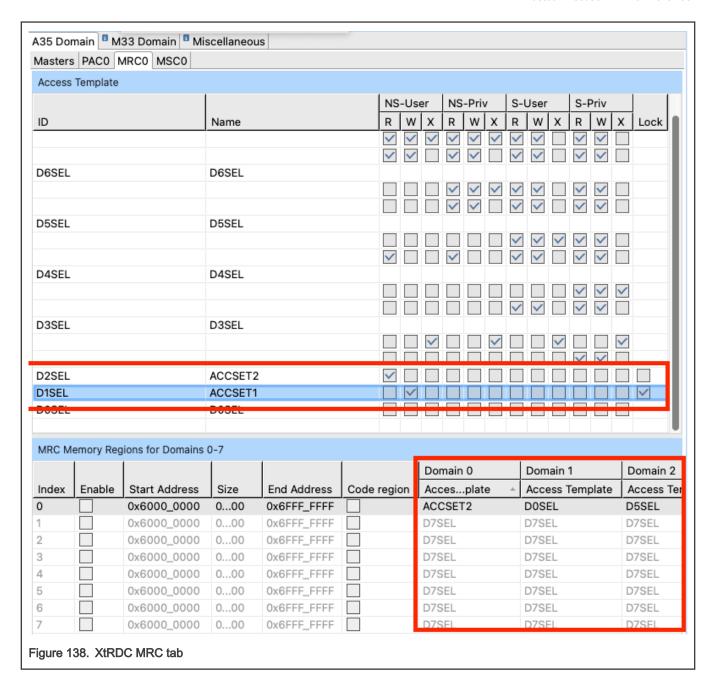

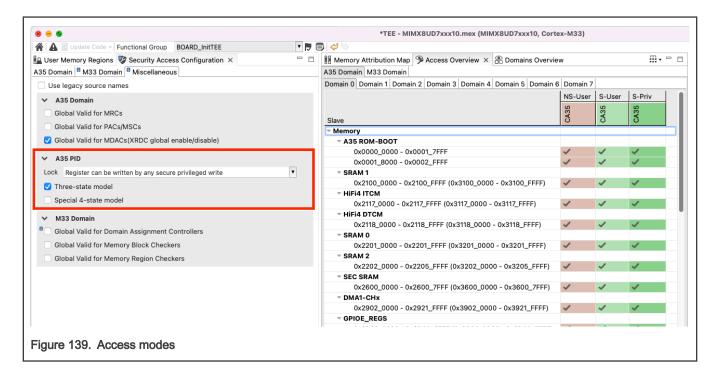

| 5.2.2.3.2 MRC                                                                        |     |

| 5.2.2.3.3 Access control modes                                                       |     |

| 5.2.2.4 Trusted Resource Domain Controller on Cortex-M33 in i.MX8 ULP and KW45 (TRI  |     |

| 5.2.2.4.1 MPU                                                                        | •   |

| 5.2.2.4.2 Domains                                                                    |     |

| 5.2.2.4.3 Masters                                                                    |     |

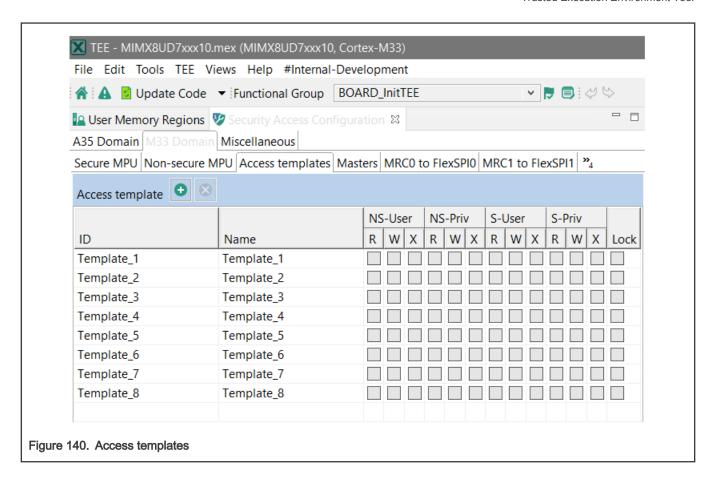

| 5.2.2.4.4 Access templates                                                           |     |

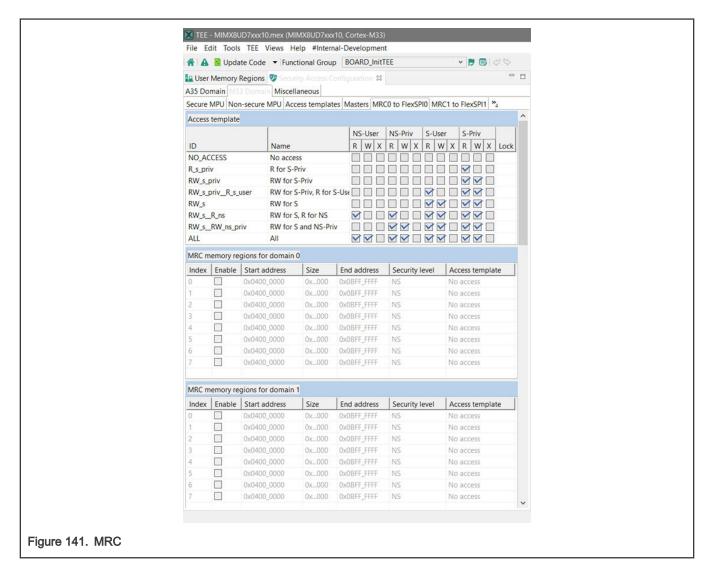

| 5.2.2.4.5 MRC                                                                        |     |

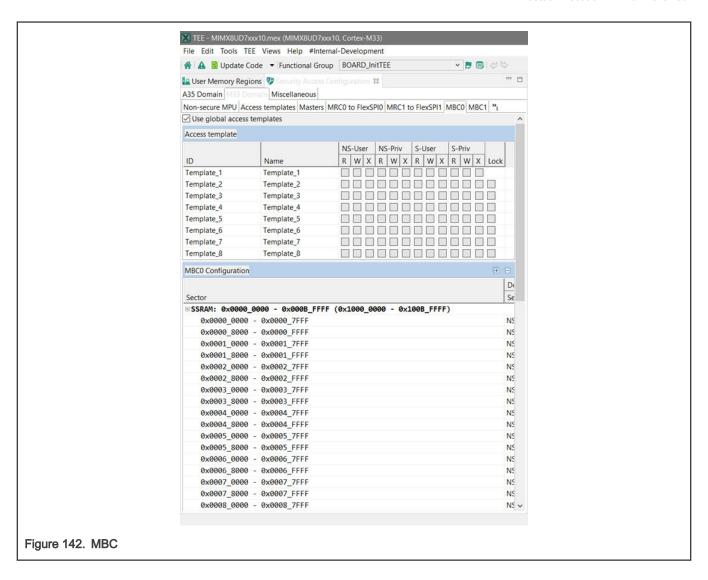

| 5.2.2.4.6 MBC                                                                        |     |

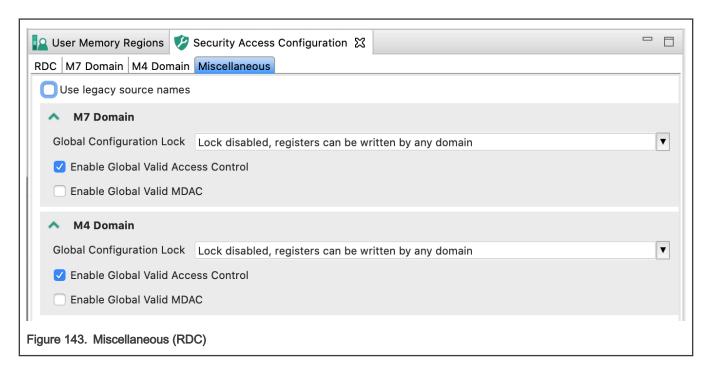

| 5.2.2.5 Miscellaneous                                                                |     |

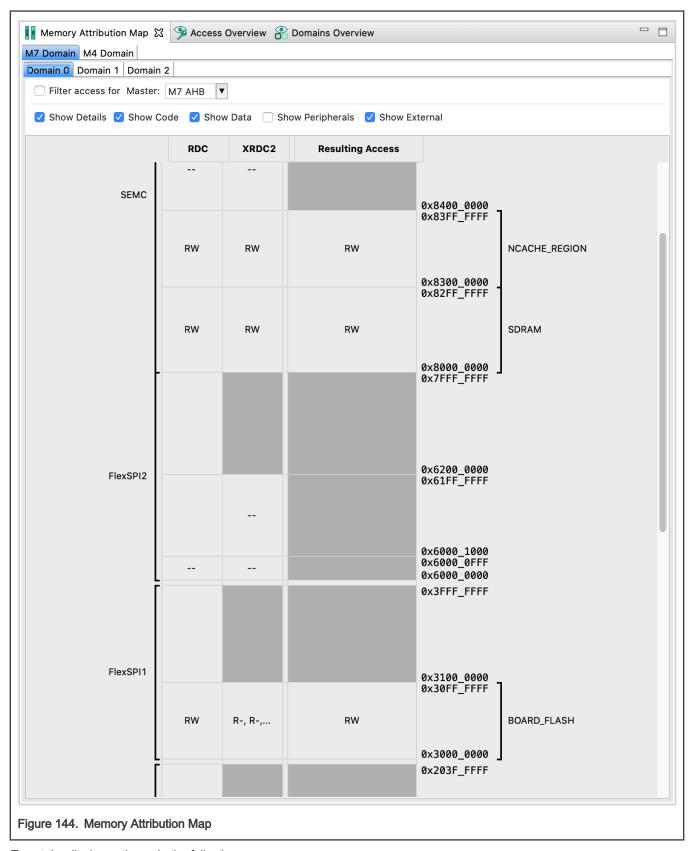

| 5.2.3 Memory Attribution Map                                                         |     |

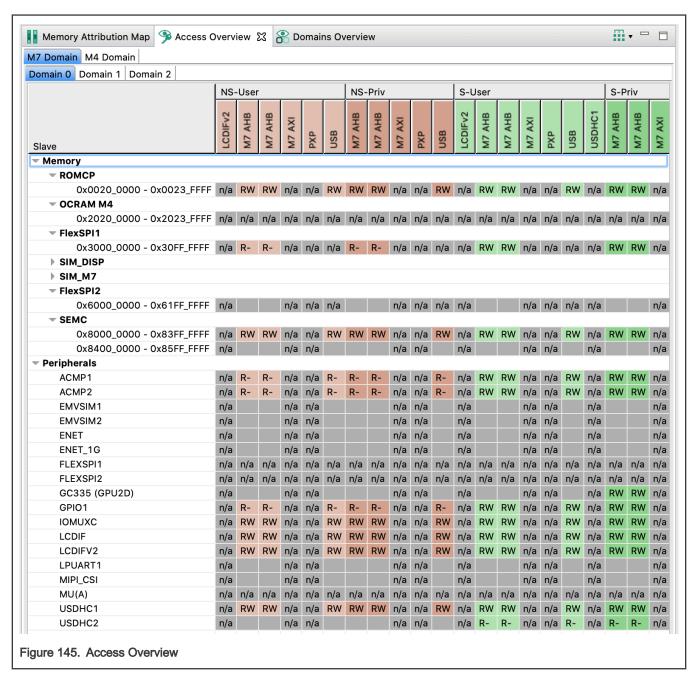

| 5.2.4 Access Overview                                                                |     |

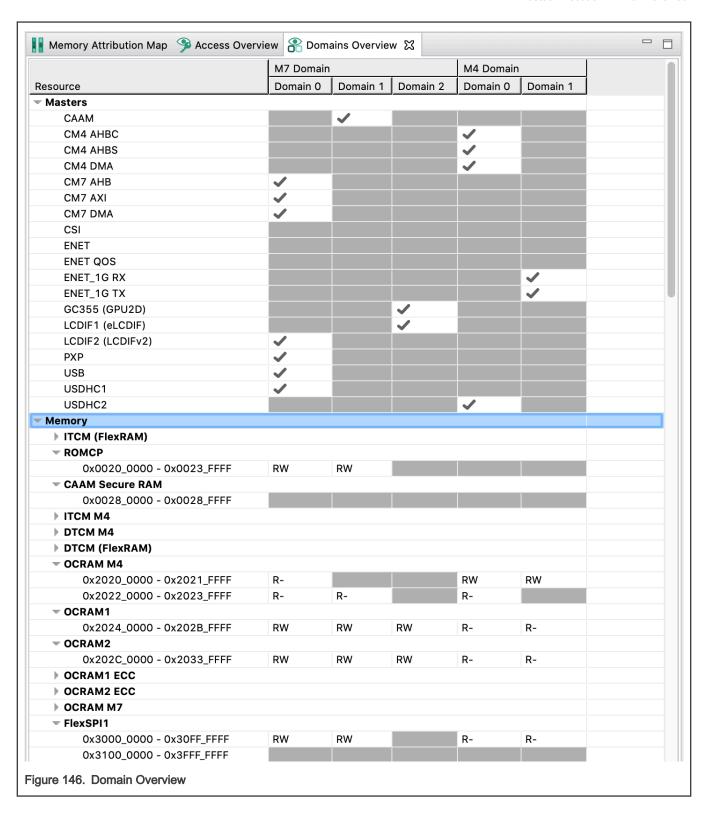

| 5.2.5 Domains Overview                                                               |     |

| 5.2.6 Code generation                                                                |     |

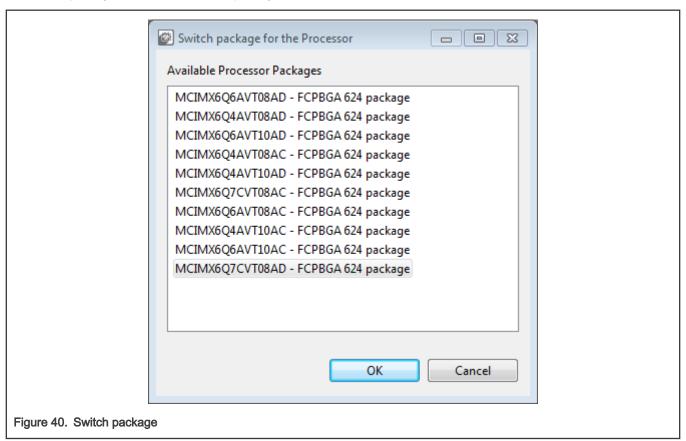

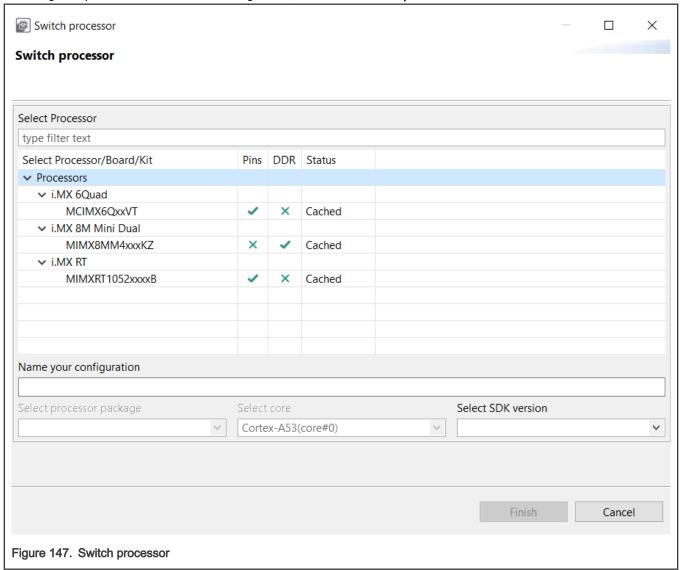

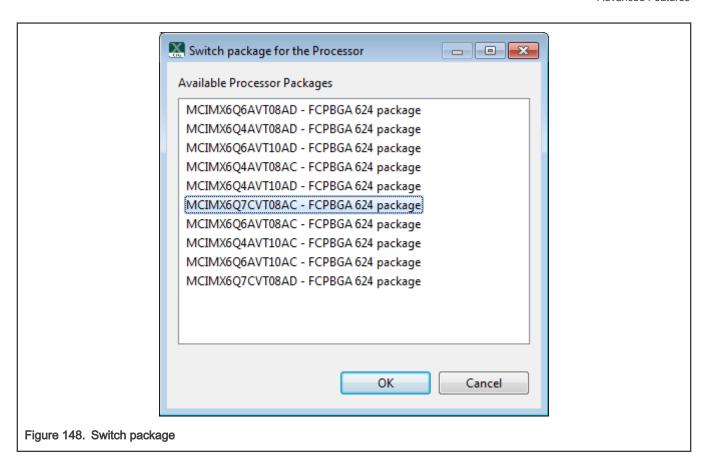

| Chapter 6 Advanced Features 6.1 Switching the processor                              |     |

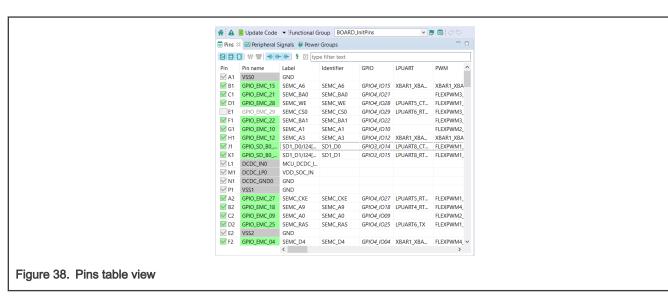

| 6.2 Exporting the Pins table                                                         |     |

| 6.3 Tools advanced configuration                                                     |     |

| 6.4 Generating HTML reports                                                          |     |

| 6.5 Exporting sources                                                                |     |

| 6.6 Exporting registers                                                              |     |

| 6.7 Managing data and working offline                                                |     |

| 6.7.1 Working offline                                                                |     |

| 6.7.2 Downloading data                                                               |     |

| 6.7.3 Exporting data                                                                 |     |

| 6.7.4 Importing data                                                                 |     |

| 6.7.5 Updating data                                                                  |     |

| 6.8 Output path overrides                                                            |     |

| 6.9 Import pins configuration from legacy tools project                              |     |

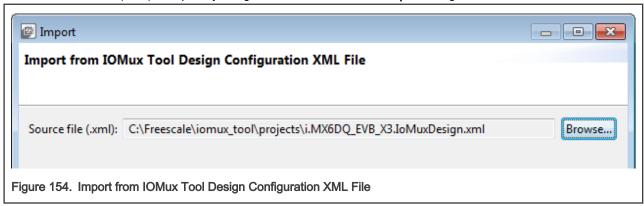

| 6.9.1 Importing from an IO Mux Tool design configuration file                        |     |

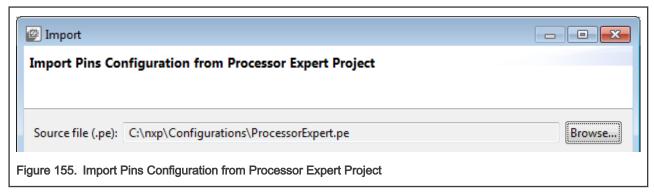

| 6.9.2 Importing from a Processor Expert project                                      |     |

| 6.10 Command line execution                                                          |     |

| 6.10.1 Command Line execution - Pins Tool                                            |     |

| 6.10.2 Command Line execution - TEE Tool                                             |     |

|                                                                                      |     |

| Chapter 7 Support                                                                    | 140 |

| , ,,                                                                                 |     |

| Chapter 8 Revision history                                                           | 141 |

|                                                                                      |     |

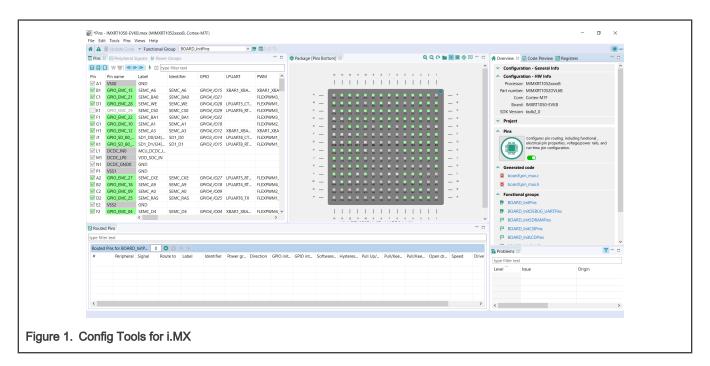

# Chapter 1 Introduction

The Config Tools for i.MX is part of MCUXpresso Config Tools, a suite of evaluation and configuration tools that help users from initial evaluation to production software development. Config Tools for i.MX is an easy-to-use way to configure the pins and DDR of the i.MX processor devices. The software, in general, enables you to create, inspect, change, and modify any aspect of the pin configuration and muxing of the device. It also allows you to configure and validate DDR settings. This document describes the basic components of the Config Tools for i.MX and lists the steps to configure and use them to configure both pins and DDR.

NOTE

Only the standalone desktop version is currently available for i.MX processors.

#### 1.1 Features

The Config Tools for i.MX consists of the Pins, TEE and DDR tools.

The Pins tool is designed for:

- · Configuration of pin routing/muxing

- · Managing different functions used for routing initialization

- · Configuration of pin functional/electrical properties

- · Generation of code for routing and functional/electrical properties

The DDR tool is designed for:

- · Configuration of DDR controllers

- · Validation of DDR configuration

The Pins tool can be used to define routing of pins for target device/board. The tool configuration may be shared using the stored configuration in the MEX file or by using the generated C or DTSI (optional) snippet files (via Import/Export or via copy-paste of the generated source).

NOTE

The Pins Tool, in general, generates code for routing the pin to the peripheral, but not for the configuration of the peripheral. Some peripherals might need additional configuration of the pin to assign function or channel. For example, for some ADC the routing provide connection between pin and the ADC peripheral. You can then assign the ADC channel from within the ADC peripheral.

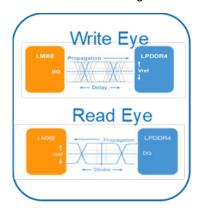

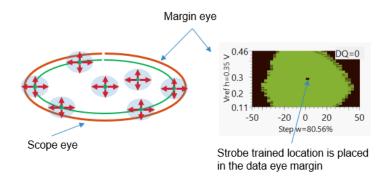

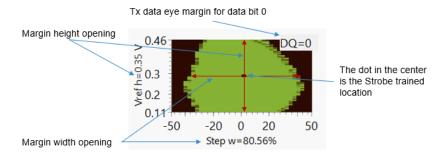

The DDR tool allows you to view and configure basic DDR attributes, such as memory type, frequency, number of channels and others and test the DDR configuration by a variety of tests. After you have specified the connection type, you can choose scenarios, tests to run in these scenarios, and view the test results, logs, and summary.

#### 1.2 Versions

For i.MX, the tool is referred to as Config Tools for i.MX and is available as a desktop application only. The tool contacts the NXP server and fetches the list of the available processors. Once used, the processors data is retrieved on demand. To use the desktop tool in the offline mode, create a configuration for the given processor while online. The tool will then store the processors locally in the user folder and enable faster access and offline use.

User Guide 5 / 145

#### 1.3 Tools localization

Tools are available in English and Simplified Chinese only.

The locale of Tools automatically copies the global settings of your computer.

To set the locale manually, add the following parameter to the command line:

tools.exe -nl zh

You can also set the locale in the tools.ini file by adding the following line:

-Duser.language=zh

#### NOTE

Setting your system locale to Chinese automatically launches the tool with localized Chinese menu items, tool tips, and help. You may need to delete the *[home\_dir]/.nxp* folder after switching languages because some menu items may be cached.

# Chapter 2 User Interface

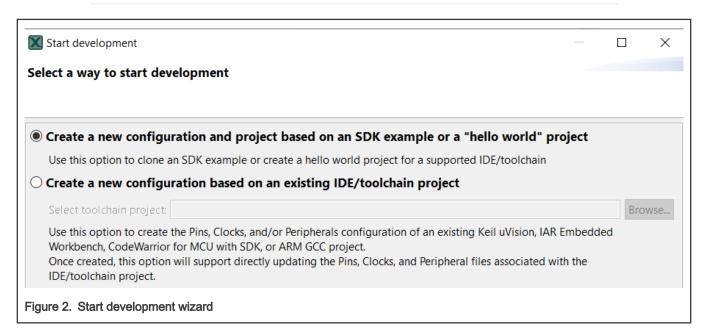

# 2.1 Start Development wizard

Upon starting Config Tools, you are automatically welcomed by a startup wizard. With this wizard, you can create a configuration or open an existing one.

NOTE

To skip the wizard on subsequent startups, select the Always open last configuration checkbox below the Open an existing configuration option. You can also perform the same action by selecting the Automatically open previously used configuration checkbox in Preferences.

NOTE

The content of this wizard is similar to the wizard that you open by selecting File > New in the Menu bar.

# 2.2 Creating, saving, and opening a configuration

In this context, configuration stands for common tools settings stored in an MEX (Microcontrollers Export Configuration) file. This file contains settings of all available tools . The folder with the saved MEX file must contain exactly one project file to be able to parse the toolchain project.

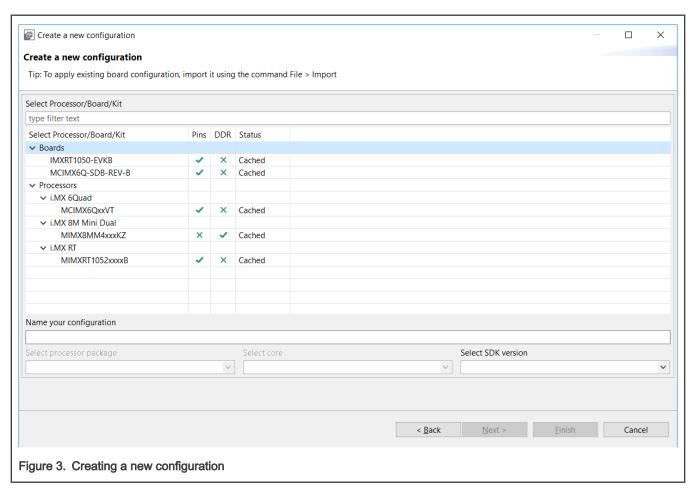

#### 2.2.1 Creating a new configuration

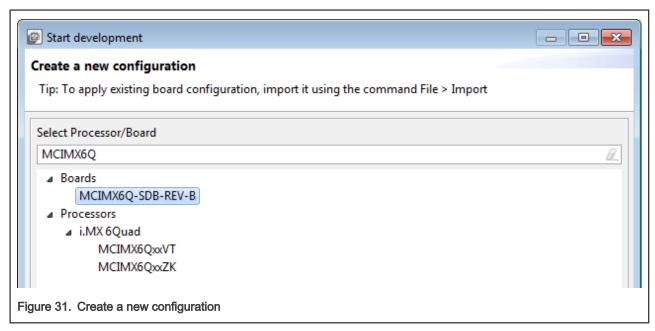

You can create a configuration from the Start development wizard or by selecting File > New from the Menu bar.

If you start creating your development for any NXP board or kit, we recommended you start with example to create a configuration for a board or a kit. Such configuration contains board-specific settings. If you select a processor, the configuration will be empty.

After the new configuration is created, you can continue by importing an existing configuration from an MEX file. It is useful if you already have a configuration available or if you want to reuse a previous configuration. To import an existing configuration from an MEX file, select **File > Import... > Import configuration (\*.mex)** from the **Menu bar**.

User Guide 7 / 145

#### 2.2.1.1 Creating a new standalone configuration

You can create a new configuration that is not part of any toolchain project.

To create a standalone configuration, do the following:

- 1. In the **Start development** wizard select **Create a new standalone configuration for processor, board, or kit**. Alternatively, in the **Menu bar**, select **File > New**.

- 2. Click Next.

- 3. Select the processor, board, or kit from the list.

NOTE

If you are working offline, you will only see locally saved options. For more information, see the Working offline section.

- 4. Name your configuration. Optionally, you can select processor package, core, and SDK version.

- 5. Click Finish.

# 2.2.2 Saving a configuration

To save your configuration for future use, select **File>Save** from the **Menu bar**.

To save a back-up of your configuration, do the following:

1. In the Menu bar, select File>Save Copy As.

9 / 145

- 2. In the dialog, specify the name and destination of the configuration.

- 3. Click Save.

The folder with the saved MEX file must contain exactly one project file to be able to parse the toolchain project.

# 2.2.3 Opening an existing configuration

To open an existing configuration, do the following:

- 1. In the Start development wizard, select Open an existing configuration. Alternatively, in the Menu bar, select File > Open.

- 2. Click Browse to navigate to your configuration file.

- 3. Select the configuration file and click Open.

- 4. Optionally, select Always open last configuration to skip the Start development wizard and load the last-saved configuration by default.

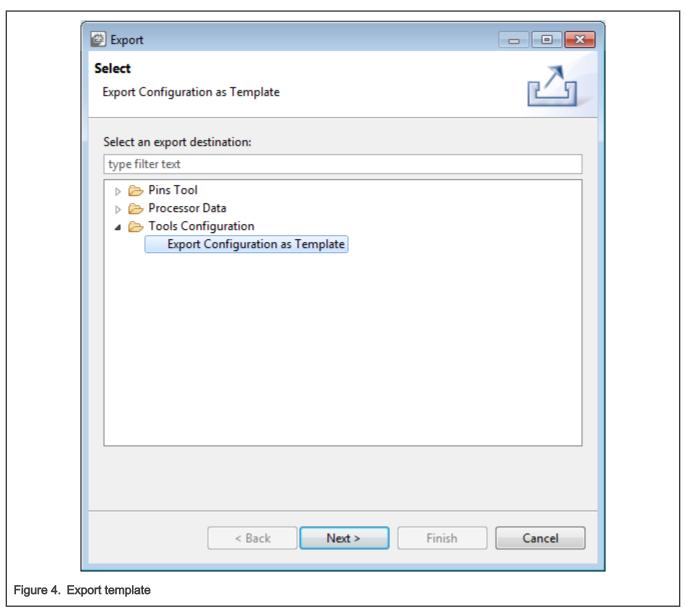

# 2.2.4 User templates

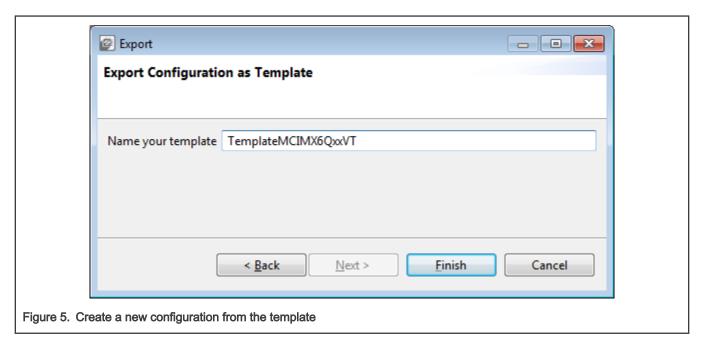

You can export and store the current configuration as a user template for later use as a reference configuration file.

User Guide

The exported template is available in the **New Configuration** wizard and can be used to create a configuration. You can also define custom labels for pins or identifiers prefixes for #define in generated code. You can export the configuration by selecting, in the **Menu bar**, **File > Export > Tools Configuration > Export Configuration as Template**.

NOTE

The templates are stored in at the following location on your local hard disk:  ${\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect}}/{\frac{\protect}{\protect$

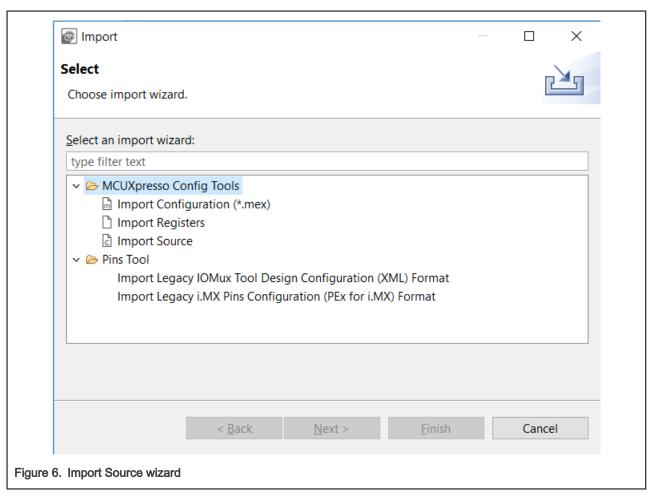

# 2.2.5 Importing sources

You can import source code files to use as basis for further configuration.

To import source code files, do the following:

- 1. In the **Menu bar**, select **File > Import...**.

- 2. From the list, select MCUXpresso Config Tools>Import Source.

- 3. Click Next.

- 4. On the next page, click Browse to specify the location of the source file.

- 5. Select the source file that you wish to import and click **Open**.

- 6. On the next page, select which functional groups to import (based on tools) by selecting the checkbox in the left column.

- 7. Define how to import the functional groups by selecting one of the two available options in the dropdown menu in the right column:

- Rename All files are merged into the current configuration. It imports all the functions only. If the imported function has the same name as an existing one, it is automatically renamed to the indexed one. For example, if BOARD InitPins exists in the configuration then the imported function is renamed to BOARD InitPins1.

- Overwrite All files are merged into the current configuration. It imports all the functions only. If the imported function has the same name as an existing one, then the existing one is replaced with the imported one.

- 8. Click Finish.

NOTE

Only C or Device Tree files with valid YAML configuration can be imported. It imports the configuration only, then the whole C file is re-created based on this setting. The rest of the C and DTSI files are ignored.

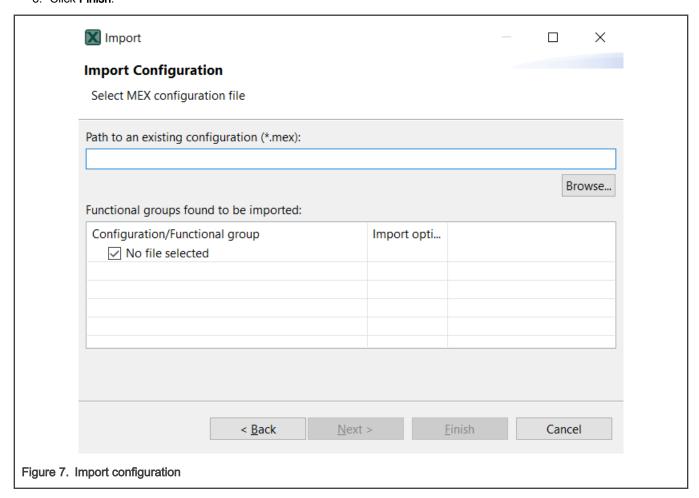

#### 2.2.5.1 Importing configuration

To import an existing configuration from an MEX file, do the following:

1. In the Menu bar, select File > Import...>.

13 / 145

- In the Import wizard, select MCUXpresso Config Tools > Import configuration (\*.mex).

- 3. Click Next.

- 4. On the next page, click **Browse** to specify the location of the registers file.

- 5. Select the MEX file that you wish to import and click Open.

- 6. On the next page, select which functional groups to import (based on tools) by selecting the checkbox in the left column.

- 7. Define how to import the functional groups by selecting one of the two available options in the dropdown menu in the right column:

- Rename All files are merged into the current configuration. It imports all the functions only. If the imported function has the same name as an existing one, it is automatically renamed to the indexed one. For example, if BOARD\_InitPins exists in the configuration then the imported function is renamed to BOARD\_InitPins1.

- Overwrite All files are merged into the current configuration. It imports all the functions only. If the imported function has the same name as an existing one, then the existing one is replaced with the imported one.

- 8. Click Finish.

# 2.2.5.2 Importing Board/Kit Configuration

Use import settings from default board/kit templates provided within CFG tools data for further configuration.

To import board/kit configuration, do the following:

1. In the Menu bar, select File > Import...>.

- 2. In the Import wizard, select MCUXpresso Config Tools > Import Board/Kit Configuration.

- 3. Click Next.

- 4. On the next page, select the board/kit variant from the dropdown menu.

- 5. Select which functional groups to import (based on tools) by selecting the checkbox in the left column.

- 6. Define how to import the functional groups by selecting one of the two available options in the dropdown menu in the right column:

- Rename All files are merged into the current configuration. It imports all the functions only. If the imported function has the same name as an existing one, it is automatically renamed to the indexed one. For example, if BOARD\_InitPins exists in the configuration then the imported function is renamed to BOARD\_InitPins1.

- Overwrite All files are merged into the current configuration. It imports all the functions only. If the imported function has the same name as an existing one, then the existing one is replaced with the imported one.

- 7. Click Finish.

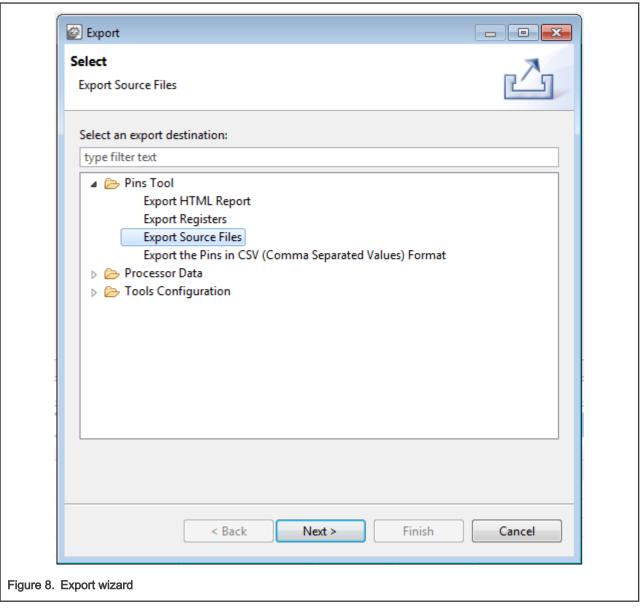

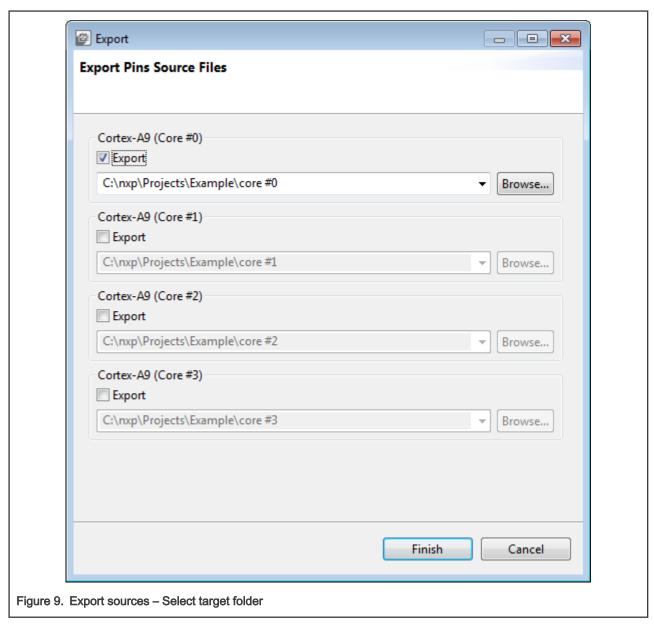

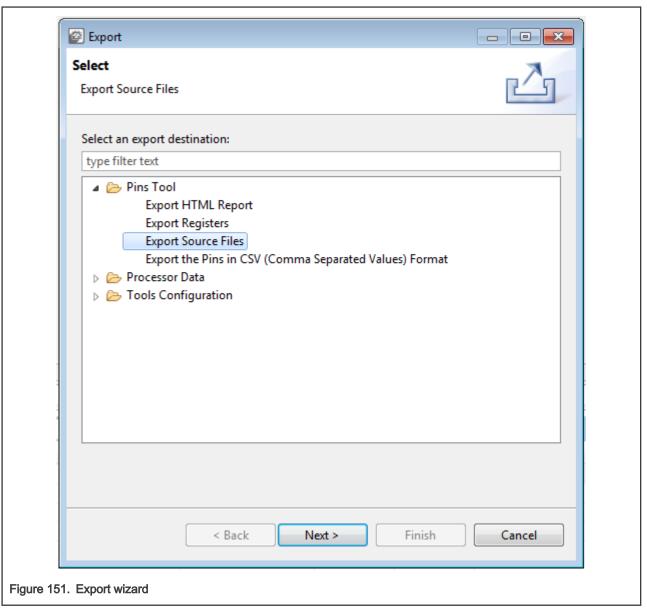

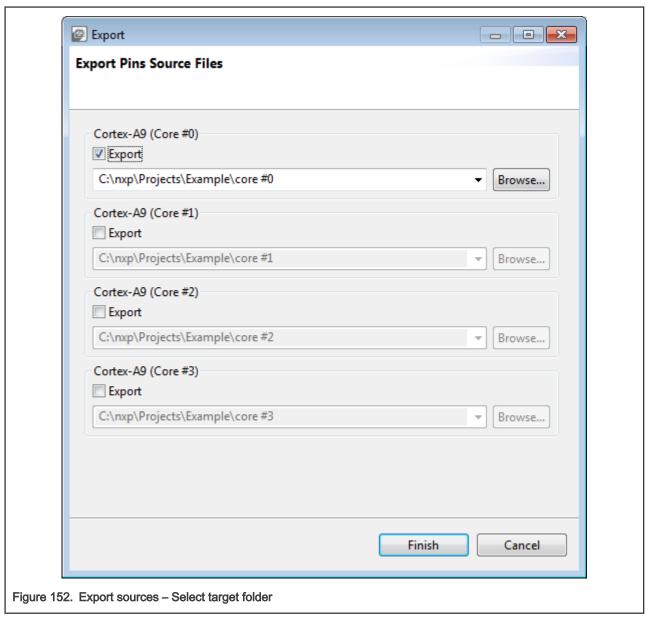

#### 2.2.6 Exporting sources

It's possible to export the generated source using the Export wizard.

To launch the Export wizard:

- 1. Select File > Export from the Menu bar.

- 2. Select Export Source Files.

- 3. Click Next.

- 4. Select the target folder where you want to store the generated files.

- 5. In case of multicore processors, select the cores you want to export.

- 6. Click Finish.

#### 2.3 Menu bar

The Menu bar contains five menus: File, Edit, Tools, Views, Help, and a tool-specific menu.

The File menu contains file management items.

Table 1. File menu

| Menu item Description |                                                                              |

|-----------------------|------------------------------------------------------------------------------|

| New                   | Create a configuration. For more information, see the Configuration section. |

| Open                  | Open a configuration from an MEX file.                                       |

Table continues on the next page...

Table 1. File menu (continued)

| Menu item        | Description                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------|

| Save             | Save current configuration.                                                                              |

| Save Copy As     | Create a backup copy of the current configuration.                                                       |

| Switch processor | Switch to a different processor. For more information, see the Switching processor section.              |

| Switch package   | Switch to a different processor package. For more information, see the Switching processor section.      |

| Select Core      | Select a processor core for further configuration.                                                       |

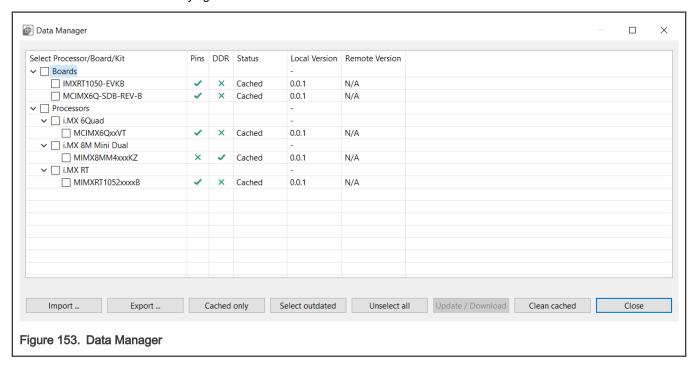

| Data Manager     | Manage local data. For more information, see the Managing data and working offline section.              |

| Import           | Import settings from source files. For more information, see the Advanced Features section.              |

| Export           | Export source files and other tool information. For more information, see the Advanced Features section. |

| Exit             | Exit the application. If there are any unsaved changes, you are prompted to save the changes.            |

The Edit menu contains basic editing actions as well as items modifying the appearance and behavior of the whole framework.

Table 2. Edit menu

| Menu item                                 | Description                                                                                        |

|-------------------------------------------|----------------------------------------------------------------------------------------------------|

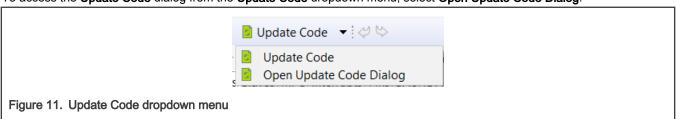

| Open Update Code Dialog                   | Update code after configuration change. For more information, see the Update code section.         |

| Undo ()                                   | Cancel a previous action. The action to be undone is always appended.                              |

| Redo ()                                   | Cancel a previous undo action. The action to be redone is always appended.                         |

| Сору                                      | Copy the selected text to the clipboard.                                                           |

| Select All                                | Select the whole text in the current field/view.                                                   |

| Call from default initialization function | Set the currently selected functional group to be called from the default initialization function. |

| Functional Group Properties               | Edit functional group properties.                                                                  |

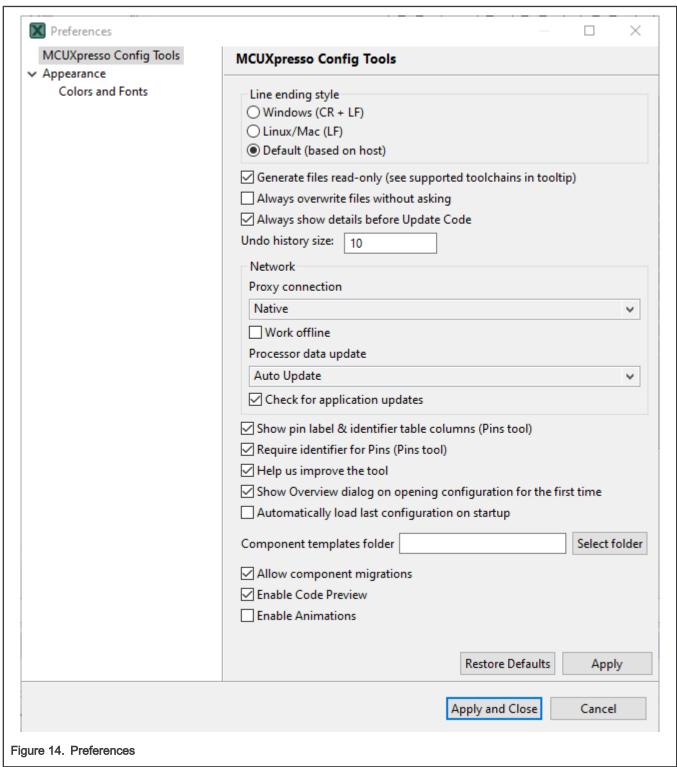

| Preferences                               | Edit preferences. For more information, see the Preferences section.                               |

| Configuration Preferences                 | Edit configuration preferences. For more information, see the Configuration Preferences section.   |

The **Tools** menu lists all the tools available in the tools framework. Use this menu to switch between the tools.

The **Tool-specific** menu contains items tailor-made for individual tools. Only items relevant to the currently active tool are displayed. The menu name copies the name of the currently active tool.

Table 3. Pins menu

| Item              | Description                       |

|-------------------|-----------------------------------|

| Functional Groups | Edit functional group properties. |

Table continues on the next page...

Table 3. Pins menu (continued)

| Item                        | Description                                                                                                                                                                      |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Automatic Routing           | Attempt to resolve routing issues. Opens the <b>Automatic Routing</b> dialog, which displays routing issues that have been resolved and the ones that require manual correction. |

| Apply Expansion Board       | Apply an expansion board to an already created expansion header                                                                                                                  |

| Create the Default Routing  | Open a dialog for the creation of a new functional group containing the after-reset state of pins and internal signals.                                                          |

| Refresh                     | Refresh both the generated code and the whole GUI.                                                                                                                               |

| Reset to Board Defaults     | Reset the configuration of the Board/Kit defaults.                                                                                                                               |

| Reset to Processor Defaults | Reset the configuration of the processor's defaults.                                                                                                                             |

The **Views** menu contains a tool-specific list of available views. Select a view from the list to open it. Select an already opened view to highlight it. Choose **Reset views** to reset the current tool perspective to its default state. The **Help** menu contains assistance and general information-related items.

Table 4. Help menu

| Item                  | Description                                                                                                                 |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Contents              | Display the User Guide.                                                                                                     |

| Quick Start guide     | Open a PDF file of the Quick Start guide.                                                                                   |

| Release Notes         | Display release notes of the installed version.                                                                             |

| Community             | Display web pages of the product-related community forums.                                                                  |

| Processor Information | Display web pages containing information about the currently used processor.                                                |

| Kit/Board Information | Display web pages containing information about the currently used board or kit.                                             |

| Open SDK API          | Display documentation of the relevant SDK API.                                                                              |

| Check for updates     | Check for a newer version of the product. If a new version is available, you are prompted to confirm and perform the update |

| Open Cheat Sheet      | Display a cheat sheet to help with using the tools. You can also load a cheat sheet from a file, or from a URL.             |

| About                 | Display general product information.                                                                                        |

# 2.4 Toolbar

The toolbar is on the top of the window and includes buttons/menus of frequently used actions common to all tools. See the following sections for more information.

Table 5. Toolbar

| Item                  | Description                                                                  |  |

|-----------------------|------------------------------------------------------------------------------|--|

| Config Tools Overview | Open the <b>Overview</b> dialog with information about currently used tools. |  |

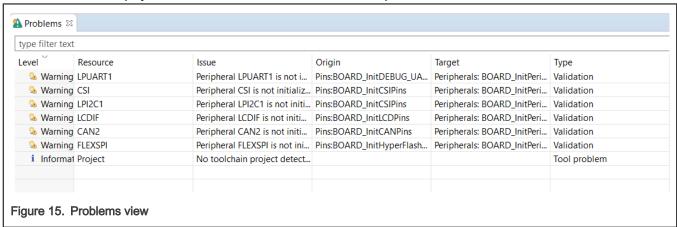

| Show Problems View    | Open the <b>Problems</b> view.                                               |  |

Table continues on the next page ...

Table 5. Toolbar (continued)

| Item                             | Description                                                                                                                                                                                                                         |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Update Code                      | Open the update dialog allowing you to update generated peripheral initialization code directly within specified toolchain project.                                                                                                 |

| Generate Code                    | Regenerate source code when "Enable Code Preview" preference is disabled.                                                                                                                                                           |

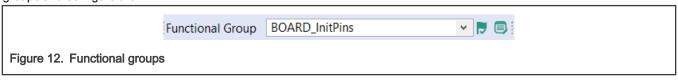

| Functional group selection       | Select functional group. Functional group in the Peripherals tool represents a group of peripherals that are initialized as a group. The tool generates a C function for each function group that contains the initialization code. |

| Call from default initialization | Set the current functional group to be initialized by the default initialization function.                                                                                                                                          |

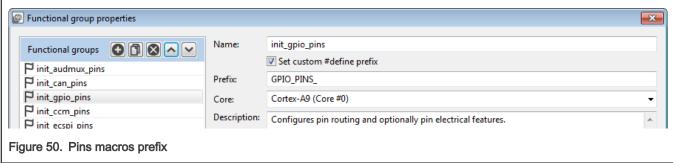

| Functional group properties      | Open the <b>Functional group properties</b> dialog to modify name and other properties of the function group.                                                                                                                       |

| Tool selection                   | Display icons of individual tools. Use them to switch between tools.                                                                                                                                                                |

| Undo/Redo                        | Undo/Redo last action.                                                                                                                                                                                                              |

In addition, the toolbar may contain additional items depending on the selected tool. See the chapters dedicated to individual tools for more information.

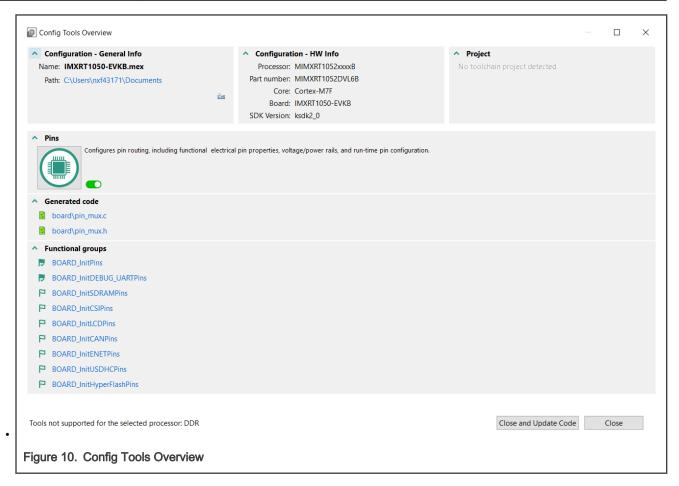

# 2.4.1 Config tools overview

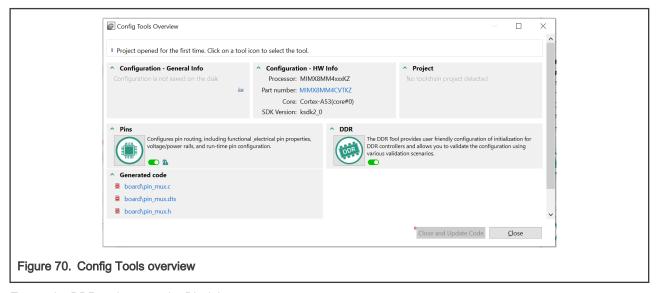

The **Config Tools Overview** provides you with general information about your currently active configuration, hardware, and project. It also provides a quick overview of the used/active and unused/inactive tools, generated code, and functional groups. By default, the **Config Tools Overview** icon is on the left side of the toolbar.

Config Tools Overview contains several items.

Table 6. Config Tools Overview

| Item                         | Description                                                                                                                                                                                                                                              |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration – General Info | Displays the name of and the path to the MEX file of the current configuration. Click the link to open the folder containing the MEX file. To import additional settings, click the <b>Import</b> additional settings into current configuration button. |